FPGA

FPGA (Field-programmable gate array, suomeksi ohjelmoitava porttimatriisi) on usean sovelluksen toteuttamiseen soveltuva järjestelmäpiiri/mikropiiri, jonka sisältämä logiikka voidaan ohjelmoida helposti uudelleen.[1][2][3] FPGA-piirit ovat kehittyneet 1980-luvulla[4] aikaisemmista ohjelmoitavista logiikkapiireistä kuten CPLD- ja PAL-piireistä, joita käytettiin järjestelmien digitaaliosien toteuttamiseen. Ohjelmoitavuuden ja useiden standardoitujen liityntävaihtoehtojen (esim. UART, I2C, SPI jne.) ansiosta FPGA-piirillä on mahdollista toteuttaa useita eri toiminnallisuuksia. FPGA-piirejä käytetään erityisesti sulautetuissa järjestelmissä, sekä yleisesti prototypointiin, pieniin ja jopa keskisuuriin tuotantosarjoihin. Aluksi FPGA-piirit eivät sisältäneet valmiita ohjelmoitavia prosessoriytimiä, mutta monipuolisimmat piirit saattavat sisältää useita prosessoreita ja niitä kutsutaankin usein FPGA-SoC-piireiksi.

FPGA-piirit ovat nopeuttaneet sulautettujen järjestelmien kehitystä, koska[5]

- ohjelmiston (SW) kehitys voi tapahtua samanaikaisesti laitteiston (HW) kehittämisen kanssa

- järjestelmän suorituskyky voidaan varmentaa laitekehityksen alkuvaiheessa

- järjestelmän toiminnallisuuden jakaminen ohjelmiston ja laitteiston suhteen voidaan tehdä osittain kokeilemalla ja tuotteistettava järjestelmäarkkitehtuuri voidaan päättää pohjautuen mittaustuloksiin simulointien lisäksi

- FPGA-piiri on ohjelmoinnin ja testauksen jälkeen valmis käytettäväksi ilman ASIC-piirin vaatimaa valmistusaikaa (engl. turn around time)

FPGA-piirit ovat välttämättömiä sellaisissa sovelluksissa, joissa standardointi kehittyy nopeasti esimerkiksi tietoliikenteessä[6],[7] tai kehitetään uutta menetelmää esim. mittauksiin, anturointiin, lääketieteelliseen kuvantamiseen[8] tai kvanttilaskennan demonstrointiin. Toiminnallisuuden (esim. salauksen, laskentakyvykkyyden jne) lisääminen olemassaolevaan ja toimivaan järjestelmään saattaa tapahtua joustavimmin ja nopeimmin FPGA-piiri(e)n avulla. Tästä esimerkkinä toimii anturien lisääminen matkapuhelimiin 2010-luvun alussa, kun käytössä olevien järjestelmäpiirien (ASIC/SoC) laskentakapasiteetti ei riittänyt käsittelemään lisääntyvien anturisignaalien laskentaan. Nopeimmat tuotteistajat lisäsivät erillisen FPGA-piirin pelkästään anturisignaalien laskentaan ja lisäsivät nopeasti järjestelmän suorituskykyä (muuttamatta järjestelmäpiiriä) ja menestystään markkinoilla. Tämän seurauksena osa anturivalmistajista myös kehitti erillisiä moduleja, jotka sisälsivät anturin lisäksi FPGA:n yleisimmillä järjestelmissä käytetyillä standardiliitynnöillä - ja vapauttivat/säästivät laskentaresursseja (engl. off-loading) järjestelmäpiireiltä. Samanlaista kehitystä tapahtuu autoteollisuudessa, puettavassa ja lentävässä/lennätettävässä elektroniikassa (UA/UAV), joissa järjestelmäpiirit ovat vasta kehtteillä tai joista on olemassa vasta ensimmäinen tuoteversio. On olemassa paljon sovelluksia (avaruus, anturointi, mittaustekniikka jne), joiden valmistusmäärät eivät tarvitse suorituskyvyn ja/tai kustannusten vuoksi parempaa integrointiastetta (ASIC/SoC/järjestelmä-/systeemipiiri) kuin FPGA.

Valtaosa FPGA-piireistä on digitaalisia, mutta myös muutamia analogista ja digitaalista signaalinkäsittelyä samalla piipalalla sisältäviä ns. sekasignaali(mixed signal)-FPGA-(SoC)piirejä on olemassa.

Myös sovelluskohtaisia (esim autoelektroniikka) sovelluspiirejä on kehitetty (esim. Gowin Semiconductor Corp). Nissä on pyritty optimoimaan ko. sovellusalueen tyypillisten/standardoitujen liitännät, käytettävissä olevat jännitteet jne, ja näin ylimääräisten toimintojen määrä verrattuna ASIC-/SoC-/systeemipiireihin jää vähäiseksi jo kehityksen alkuvaiheessa.

Haittoja

Suurimpia haittapuolia FPGA-piirien käytöstä tuotannossa saattaa olla

- Ylimääräinen tehonkulutus johtuen mahdollisista valitun FPGA-pohjan ylimääräisistä lohkoista/toiminnallisuuksista verrattuna sovelluksen vaatimiin tarpeisiin. Useimmiten äärimmäinen tehonkulutuksen minimointi vaatiikin ASIC-piiritoteutuksen FPGA-vaiheen jälkeen. FPGA-pohja joudutaan usein valitsemaan noin max 80% johdotustäyttösuhteen mukaan, koska lohkot ovat valmiiksi paikoitettuja piille ja on varmistettava johdotuksen onnistuminen. Uuden FPGA-pohjan valinta kesken piirin suunnittelun ja testauksen saattaa johtaa aikatauluviiveisiin toteutuksessa.

- Äärimmäistä nopeutta saattaa olla vaikea saavuttaa ilman huomattavaa tehonkulutuksen lisäystä ja mahdollisesti siitä johtuvaa järjestelmän ylimääräistä lämpenemistä ja sen vaatimia lämmönpoistotoimenpiteitä

- Kasvavissa tuotantovolyymeissa FPGA:n hinta saattaa osoittautua ASIC-toteutusta kalliimmaksi. Koska ASIC-piirin toteus vaatii suunnittelu-, testaus- ja valmistusaikaa ja mahdollisesti uusia toimittajia tuotantoketjussa, on siirtyminen FPGA-piiristä ASICiin suunniteltava huolellisesti etukäteen, jos tuotantovolyymit kasvavat. Ajoituksen epäonnistuminen voi johtaa hinta-/suorituskilpailukyvyn nopeaan menettämiseen.

- Useita FPGA-piirejä sisältävissä järjestelmissä siirtyminen ASIC/SoC-systeemi/järjestelmäpiireihin voi tapahtua piiri/toiminnallisuus kerrallaan, ja tämä saattaa vaatia useiden kuukausien/yli vuoden kehitys-/tuotteistusajan käytännössä, mutta mahdollistaa optimaalisen suorituskyvyn ja kustannukset/hinnan järjestelmän eri tuotanto- ja kehitysvaiheessa.

Valmistajia

Merkittävimpiä digitaalisia FPGA-ja FPGA-SoC piirivalmistajia ovat

- AMD (Xilinx[9],[10]) [11]

- Achronix[12]

- Intel (ent. Altera)[13]

- Lattice Semiconductor[14]

- Microchip Technology (ml. Microsemi) [15]

- Quicklogic[16]

Sekasignaali-FPGA-Soc-piirejä on Infineonilla (ent. Cypress Semiconductor Corp:n ns. PSOC-/Programmable System on Chip-tuoteperhe)[17] ja Microsemilla (ns Fusion-tuoteperhe)[18]. Tosin analogisten ja analogis-digitaalisten osien suorituskyky (esim. muunninten resoluutio ja nopeus) saattaa olla rajoittunutta. Useissa sovelluksissa kuitenkin esimerkiksi 10-12 bitin muunninten resoluutio ja/tai samalla piipalalla (engl. chip) oleva langaton yhteyslohko/-toiminto voi mahdollistaa kokonaan uuden tuotteen tai tuotekategorian.

Valmistusteknologiat

FPGA-piirit valmistetaan yleisimmin CMOS-teknologialla, johon on lisätty erilaisia muistioptioita (OTP engl. One Time Programmable, NVM engl. Non-Volatile Memory jne.) lisääviä valmistusaskelia, ja substraattina käytetään puolijohtavaa piitä. FPGA-piirien valmistusteknologiat ovat yleensä 1-3 sukupolvea jäljessä tiheimpien tuotanto-ASIC/IC-piirien valmistusteknologioista, ja siitäkin syystä ne ovat esim. hitaampia, mutta valmistuskustannuksiltaan halvempia kulutettua piin pinta-alaa kohti.

Myös eristävälle substratille valmistettuja (FD-SOI Fully Depleted Silicon on Insulator) FPGA-piirejä on julkaistu[19] tehonkulutuksen minimoimiseksi ja häiriömarginaalien parantamiseksi. Tavoitteena on myös ollut säteilynkeston parantaminen esim. avaruussovelluksiin.

Käyttö ja ominaisuudet

FPGA-piirejä verrataan usein sovelluskohtaisiin mikropiireihin (ASIC ja SoC - System on Chip), sillä niiden sovellusalueet ovat usein samoja. FPGA-piirien suunnittelu poikkeaa huomattavasti esimerkiksi ASIC-piirien suunnittelusta.[20] FPGA-piiriin verrattuna ASIC/SoC kuluttaa yleensä vähemmän tehoa ja sitä kautta lämpenee vähemmän, koska kaikki ylimääräiset liitännät ja elementit on karsittu pois. Yleensä FPGA-toteutus vie enintään n. 80% käytettävistä toiminnoista, mikä mahdollistaa toimintojen muuttamisen suunnittelun loppuvaiheessa esimerkiksi standardoinnin kehittyessä tai asiakastarpeiden muuttuessa. Vaikka ASIC/SoC on yleensä pienikokoisempi ja maksaa suurissa erissä vähemmän kuin saman toiminnalisuuden FPGA, suunnittelun ja koepiirien tuottaminen on huomattavsti nopeampaa. Näistä syistä sulautettujen laitteistojen tuotekehityksessä alkuvaiheessa käytetään FPGA-piirejä ja siirrytään ASIC/SoC-piirien käyttöön, kun tuotantomäärät kasvavat. Koska siirtyminen ASIC/SoC-piireihin ei tapahdu ilman uudelleen suunnittelua, valmistusta ja testausta, on siirtymisajankohta FPGAsta ASICiin/SoCiin määriteltävä siten, että ASIC/SoC-piirien mahdolistavat suorituskykylisäykset ja taloudellinen tehokkuus toteutuvat käytännössä. On huomattava, että siirtyminen FPGA:sta ASIC/SoC-piiriin tai joskus -piireihin vaatii tavallisimmin muutoksia myös useisiin muihinkin järjestelmän osiin kuten mm. tehontuottoon/käyttöjännitteisiin, kellotukseen, järjestelmäpiirilevyyn, testattavuuteen, mahdollisesti tarvittavaan salaukseen ja jopa tuotteen mekaaniseen ratkaisuun.

Ennen FPGA-piirien suunnittelua on valittava soveltuva valmistaja ja tuoteperhe. Tärkeimpiä valintakriteereitä ovat[21]

- Suorituskykyvaatimukset (nopeus, tehonkulutus)

- Ulkoisten liityntöjen määrä, liityntävaatimukset (LVCMOS, LVDS, LVTTL, HSTL jne.) ja niiden yleiskäyttöisyys

- Muisti(e)n (SRAM, OTP, NVM jne.) koko

- Kehitysympäristön (ohjelmisto ja laitteisto) saatavuus,ja valmistajan tuki yleisesti ja eriyisesti standardiliityntöjen osalta: ovatko liitynnät (esim I2C, SPI jne) saatavana kiinteinä (hard macro) vai SW-muodossa (soft macro)

- Mahdollisten maksullisten (ohjelmisto)lisenssien välttämättömyys kehitysvaiheessa ja tuotannollistamisessa joskus jopa kolmannelta osapuolelta

- Fyysinen koko ja piirin/piirien eri kotelontimahdollisuudet

- Valmistajan kyky tuottaa piirejä mahdollisesti kasvavissa määrin taloudellisesti

- Kovetus-/jäädytysmahdollisuudet (engl. hardening/freezing) eli siirtyminen suorituskyvyltään vähintään vastaavaan/lopulliseen ASIC/SoC-piiriin, mikäli on odotettavissa tuotantomäärien kasvua. Muutamat FPGA-piirivalmistajat ovat solmineet sopimuksia piivalimoiden kanssa varmistaakseen joustavan siirtymisen FPGAsta ASICiin/SoCiin, jos omaa valmistuskapasiteettia ei ole tai se ei riitä ASIC/SoC-tuotantomääriin

- Jos kyseessä on FPGA-SoC-piiri, mitä valmiita ytimiä/IP-lohkoja on käytetty piiripohjassa, ja miten niiden suorituskyky ja siirtäminen ASICin osaksi käytännössä varmistetaan (ml. käyttölisenssit)

- Kyseessä olevan FPGA:n/-piiriperheen/-valmistajan oma ja mahdollinen käyttäjä-/harrastajayhteisön tuki

Sekasignaali-FPGA-piiriä valittaessa on lisäksi selvitettävä ovatko piirin mahdollisten muunninten suorituskyky riittävä ja mitä muita analogisia/analogis-digitaalisia lohkoja (esim. lämpötilamittaus, kosketusanturien kontrollointi jne.) tai langattomia yhteys- (esim. bluetooth) ja salauslohkoja on saatavilla integroituna FPGA:han.

Kun laitteistokuvauskielellä kirjoitettu malli on syntetisoitu, se voidaan suoraan ladata piirille ja aloittaa käyttö siinä missä ASIC-piirin kanssa alotettaisiin vasta piirin valmistukseen tähtäävä suunnittelutyö. Kriittisin vaihe FPGA:n suunnittelussa on yleensä ajoitusten simulointi,ja hyväksyminen (engl. timing closure). Kun laitteistokuvaus ajoituksineen ja hyväksytty,laitteistokuvaus voidaan tallettaa pieneen oheispiiriin/muistiin, josta se automaattisesti syötetään FPGA-piiriin aina kun laite käynnistetään. Heti tämän jälkeen itse FPGA aloittaa toimintansa.

FPGA-piirien kasvaessa toteutuvan ajoituksen testaaminen saattaa kerralla koko piirille olla vaativa tehtävä. Siksi on kehitetty FPGA-piirejä, joissa ajoituksen hyväksyminen voidaan tehdä osittain lohkoille, joita kutsutaan verkkoalueiksi (engl. NoC, Network on chip), ja näin nopeuttaa ajoituksen testausta ja hallintaa[22].

Mallissa havaittujen suunnitteluvirheiden korjaus on helppoa vaatiessaan vain uuden syntetisoinnin ja piirin uudelleenohjelmoinnin. Tämän takia FPGA-piirit sopivat erityisesti ASIC-piirien prototyypitykseen, sekä laiteajuri- ja firmwarekehitykseen siksi ajaksi ennen kuin varsinainen ASIC-piiri on valmis. FPGA-piirejä käytetään myös tilanteissa joissa piirin sisältävää laitetta valmistetaan pieni kappalemäärä jolloin kappalehinnalla ei ole suurta merkitystä, kokoa ja tehonkulutusta ei tarvitse minimoida, logiikan uudelleenohjelmoitavuus ja virheiden korjaus tuotteen toimituksen jälkeen on välttämätöntä, tai laite halutaan mahdollisimman nopeasti markkinoille.

Piirin toiminnan suunnitteluun jokainen FPGA-piirin valmistaja tarjoaa oman alustakohtaisen ohjelmiston. Yleensä ohjelmisto on saatavilla Windows- ja Linux-käyttöjärjestelmille ja se on ominaisuuksiltaan erittäin monipuolinen. Arvokkaiden yrityslisenssien lisäksi suunnitteluohjelmistoista julkaistaan yleensä myös pieniä rajoituksia sisältävä ilmaisversio.

FPGA-piirien ympärille on syntynyt myös järjestelmävalmistajia, jotka ovat valmiiksi integroineet FPGA-piirin oheistoimintoineen valmiille piirilevylle ja mähdollistavat tuotekehityksen nopean aloituksen.

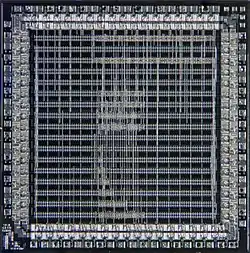

Rakenne

FPGA-piiri koostuu geneerisistä logiikkaelementeistä, joiden toteuttama kombinatorinen logiikka ja väliset kytkennät ovat ohjelmoitavissa. FPGA-piirin valmistaja ilmoittaa yleensä logiikkaporttimäärän jota vastaavan toiminnallisuuden piiri pystyy parhaimmillaan toteuttamaan. Nykyaikaisissa piireissä tämä määrä lasketaan sadoissa tuhansissa porteissa. Käytännössä tästä maksimimäärästä jäädään usean kymmenen prosentin päähän, sillä ohjelmoitavien logiikkaelementtien välinen reititys piirillä optimaalisella tavalla on erittäin vaikeaa. Pitkät reitit logiikkalementtien välillä myös rajoittavat kellotaajuutta jolla piiriä voidaan käyttää. Mikäli logiikkaportteja tarvitaan enemmän kuin mihin yksi piiri pystyy, on useamman FPGA-piirin yhteiskäyttö mahdollista joillain alustoilla.

FPGA-piiri saattaa sisältää myös ei-ohjelmoitavia osia esimerkiksi usein käytettyjä aritmeettisia operaatioita varten, digitaalisia suotimia ja muita vastaavia suhteellisen yksinkertaisia piirejä, muistia, tai joskus jopa kokonaisia yleiskäyttöisiä ohjelmoitavia suorittimia. Näiden avulla piirin suorituskykyä ja tehonkulutusta voidaan parantaa. Prototyypitystä varten FPGA-piirejä saa myös piirilevyillä, joilla on valmiina muita mahdollisesti hyödyllisiä piirejä ja muuta elektroniikkaa, kuten A/D-muuntimia, muistipiirejä, näyttöjä, kytkimiä, liittimiä yms. Lopputuotteessa FPGA-piirin ohjelmointidata saattaa olla tallennettuna haihtumattomalle muistille josta se ladataan FPGA-piirille laitteen käynnistyessä.

Katso myös

- ASIC (Application Specific Integrated Circuit)

- EPLD (Erasable programmable logic device)

- PAL (Programmable array logic)

- GAL (Generic array logic)

- Laitteistokuvauskieli

- Logiikkasynteesi

- Mikropiiri

- Digitaalipiirit

Lähteet

- P.-K. Poiksalo: Digitaalitekniikan Perusteet: aloitusopas digitaalisen maailman rakentajille, 256 s.. Microdim Finland, 2019.

- P. Korpinen: Lis. työ, Using reconfigurable hardware to distribute network traffic for parallel processing, 95 s. Teknillinen Korkeakoulu. 2009. Viitattu 3.5.2020.

- C. Maxfield: Fundamentals of FPGAs and why they are needed Digikey articles. 14.11.2019. Viitattu 2.5.2020.

- "Three ages of fpgas: A retrospective on the first thirty years of fpga technology" (2018). IEEE Solid-State Circuits Magazine 10 (2): 16-29.

- P. A. Simpson: FPGA Design, Best Practices for Team Based Reuse, 2. painos, s. 16. Springer International Publishing AG, 2015.

- H. Räbinä: Creating a reusable FPGA programming model architecture for 5G layer 1, 75 s. DI-työ, Aalto Yliopisto. 2019. Viitattu 5.5.2020.

- V. Seppänen: Partially reconfigurable SDR solution on FPGA DI työ, Oulun Yliopisto. 2019. Viitattu 5.5.2020.

- D. G. Bailey: Image Processing Using FPGAs, 204 s.. MDPI AG, 2019.

- C. Maxfield: Fundamentals of FPGAs, Part 4 Digikey articles. 1.4.2020. Viitattu 5.5.2020.

- J. Salmela: Xilinxin 7-sarjan FPGA-piirien muistiresurssit ja niiden käyttö suunnittelussa, 26 s. Kandidaattityö, Oulun Yliopisto. 2019. Viitattu 5.5.2020.

- AMD: AMD:n Xilinx osto valmis 14.2.2022. AMD. Viitattu 21.3.2022.

- Achronic: Achronix FPGAs Achronix web-site. Viitattu 11.5.2020.

- Intel: Intel FPGAs Intel web-site. Viitattu 5.5.2020.

- C. Maxfield: Fundamentals of FPGAs, Part 2 Digikey articles. 18.12.2019. Viitattu 3.5.2020.

- C. Maxfield: Fundamentals of FPGAs, Part 3 Digikey articles. 30.1.2020. Viitattu 5.5.2020.

- Quicklogic: Quicklogic FPGAs Quicklogic web-site. Viitattu 9.5.2020.

- Cypress PSOC Mouser. Viitattu 5.5.2020.

- Microsemi Fusion web-linkki. Viitattu 7.5.2020.

- Eetimes: Lattice Unweils first FPGAs on FD-SOI Article. 2019. Viitattu 3.5.2020.

- Turo Id: Mikroprosessorijärjestelmän suunnittelu FPGA:lla Opinnäytetyö. 2018. Vaasan ammattikorkeakoulu. Viitattu 21.3.2022.

- R. C. Cofer, B. Harding: Rapid System Prototyping with FPGAs, 295 s.. Elsevier, 2006.

- M. Ijaz: Implementation of NoC on FPGA with Area and Power Optimization web-linkki. 2019. Viitattu 9.5.2020.

Aiheesta muualla

- I. Lankshear: 5G Cellular Infrastructure and the Migration from FPGAs to Custom ASICs Electronic Design www.electronicdesign.com. 7.10.2019.

- Esitykset aiheesta 'FPGA' viimeisen vuoden aikana SlideShare.net:ssä slideshare.net.