Fasean lotutako begiztak

Fasean lotutako begiztak edo PLL (ingelesetik, Phase-Locked Loops) 60. hamarkadatik elektronikan sarri erabilitako elementuak dira. Birrelikatutako sistema bat da, non birrelikatutako magnitudeak maiztasuna eta fasea diren.

Historia

PLLak lehen aldiz 60. hamarkadan erabili ziren, NASAk satelite bidezko komunikazioetan elementuen ezegonkortasuna eta Doppler efektuaren ondorioz agertzen ziren maiztasun aldaketei aurre egiteko.

Funtzionamendua

Helburua erregimen iraunkorrean sarrera eta irteerako seinaleen faseak "lotuta" egotea da, maiztausna bera delarik. PLL bat lotuta dagoela diogu sarrerako maiztasunaren (fe) margen batzuen barneko aldaketa baten aurrean, irteerako maiztasunak (fs) berdindu arte eboluzionatzen duenean.

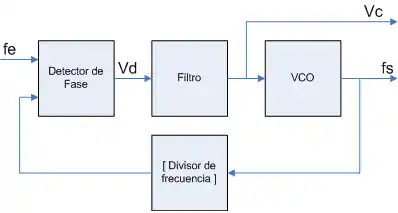

Bere funtzionamendua honakoa da:

- Fase detektoreak bere irteeran (Vd) tentsio bat jasotzen du, sarrerako bi seinaleen faseen proportzionala.

- Behe pasa iragazkiak PLL mota eta bere ezaugarriak determinatzen ditu

- Tentsioak kontrolatutako osizladoreak irteera bezala sarrerako tentsioaren (Vc) proportzionala den irteerako frekuentzia bat (fs) itzultzen du.

Normalean guztia chip berean enkapsulaturik aurkitu dezakegu, iragazkia izan ezik, honek kontrolatuko baititu PLLaren ordena eta bere lan eremuak.

Zenbait konfigurazioetan frekuentzia zatitzaile bat erabiltzen da birrelikaduran, irteeran sarrerako frekuentziaren multiplo bat izateko.

PLL demoduladore moduan erabilztean irteera modura iragazkiaren irteera hartzen da (Vc).

Analisia

PLLdun zirkuituak bi eratan aztertzen dira:

- Azterketa lineala, osagai lineal guztiak kontuan hartuz eta PLL hasieran lotuta kontsideratuz.

- Azterketa ez-lineala

Lan tarteak

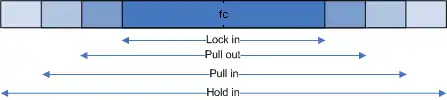

PLL lotuta egongo den baldintzak definitzen dituzte, lortzea zenbat denbora emango duen eta zein baldintzapean askatzen den.

Hold in

PLLa lotuta dagoela kontsideratuz. PLLak sarrerako maiztasunaren aldaketa geldoak jarraitzeko gai den maiztasunen tartea.

Pull out

Sarrerako maiztasunaren aldaketa bortitz bat gertatzean PLL askatzen ez den maiztasun tartea.

Lock in

PLL askatuta dagoela kontsideratuz. Irteera maiztasunaren periodoa baino denbora gutxiagoan lotzeko gai den maiztasunen tartea.

Pull in

PLLak irteera periodoa baino denbora luzeagoan lotzea lortzen duen maiztasun tarteari deritzo.

Irudian maiztasun tarteak agertzen dira. Guztiak erdiko frekuentzia den osziladorearen oszilazio maiztasun librearen inguruan agertzen dira.

Aplikazioak

- AM eta FSK seinaleen demodulazioa.

- Jarraipen iragakiak

- Osziladore oso egonkorrak

- FM seinaleen modulazio eta demodulazioa

- Maiztasun sintezizatzaileak

Ikus, gainera

Kanpo estekak

- Zer da PLL bat? (ingelesez)

- AN535 (pdf)