EZ-ETA ate logikoa

EZ-ETA edo NAND ate logiko bat da, irteera faltsu bat eragiten duena soilik bere sarrera guztiak egiazkoak badira; beraz, bere irteera, ETA ate logikoaren osagarria da, -eskuinean erakutsitako benetako taularen arabera jokatzen du-. Sarrera guztiak 1ean (bat) edo altan daudenean, irteera 0an edo bajan egongo da; aldiz, sarrera bat edo biak gutxienez 0an edo bajan daudenean, irteera 1ean edo altan egongo da.

| SARRERA A B | IRTEERA A EZ-ETA B | |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Ikurrak

Ikurrak irudikatzeko bi modu daude, lehenengoa "ikur militarra"rekin eta bigarrena, berriz, "ikur angeluzuzena"rekin:

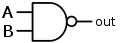

EZ-ETA ikur militarra (ANSI)

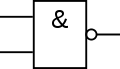

EZ-ETA ikur militarra (ANSI) EZ-ETA Ikur angeluzuzena (Europarra)

EZ-ETA Ikur angeluzuzena (Europarra)

Hardwarearen deskribapena

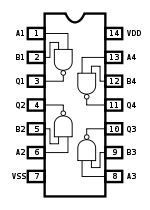

EZ-ETA ate logikoak TTL zein CMOS zirkuitu integratuekin bateragarriak dira. CMOS 4000 serieko EZ-ETA ate logiko estandarra 4011 zenbakiduna da. 4011k bi sarrerako lau ate logiko independente dakartza (ikus bedi irudia).

Sarrera gehiagoko EZ-ETA ate logikoak nahi baditugu ondorengo CMOS zirkuitu integratuetara jo dezakegu:

- 4023: 3 Sarrerako hiru EZ-ETA ate logiko.

- 4012: 4 Sarrerako bi EZ-ETA ate logiko.

- 4068: 8 Sarrerako EZ-ETA ate logiko bat.

TTLn, berriz:

- 7400: 2 Sarrerako lau EZ-ETA ate logiko.

- 7410: 3 Sarrerako hiru EZ-ETA ate logiko.

- 7420: 4 Sarrerako bi EZ-ETA ate logiko.

- 7430: 8 sarrerako EZ-ETA ate logiko bat.

Inplementazioa

EZ-ETA ate logikoak egiteko ate logikorik errezenak dira, horrexegatik ate logiko hauek beste funtzio logiko guztiak betetzeko erabiltzen dira.

EZ-ETA funtzioa NMOS 1 transistoreekin inplementatu daiteke.