Zweiter Durchbruch

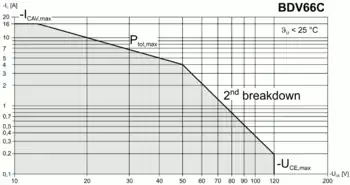

Als zweiter Durchbruch (englisch secondary breakdown) wird eine besondere Form der Überlastung eines Bipolartransistors durch zu hohe Spannung (Sperrspannung über der Kollektor-Emitter-Strecke) bezeichnet.

Erhöhung der Sperrspannung durch negative Basisspannung

Bauartbedingt besitzt jeder Bipolartransistor eine bestimmte, maximal zulässige Sperrspannung über der Kollektor-Emitter-Strecke bei unbeschaltetem Steueranschluss (Basis). Gemeinhin wird dieser Wert mit dem Parameter UCEO bezeichnet. Wird dieser Wert von der angelegten Spannung überschritten, kommt es zum sogenannten „ersten Durchbruch“, bei welchem das Bauelement, ähnlich dem Verhalten einer Z-Diode, beginnt zu leiten. Solange in diesem Fall nicht die zulässige Temperatur überschritten wird, ist ein erster Durchbruch bei den meisten Transistoren unschädlich.

Wird ein solcher Transistor an seiner Basis aber solcherart vorgespannt, dass diese in Sperrrichtung betrieben wird (negativ bei einem npn-Transistor und positiv beim pnp-Pendant), so sind die meisten Typen dazu in der Lage, deutlich höhere Spannungen zu sperren. Der Gewinn an Sperrspannung kann ca. 50 % betragen. (Nur Bipolartransistoren können auf diese Weise „getunt“ werden. MOSFETs z. B. bieten diese Möglichkeit nicht.) Diese maximal mögliche Sperrspannung bei solcherart betriebenen Transistoren wird mit dem Parameter UCE,r oder UCB0 in den Datenblättern angegeben.

Erst wenn ein so gesperrter Transistor in einem Fehlerfall durch zu hohe Spannung zum Leiten gebracht wird, tritt der sogenannte „zweite Durchbruch“ auf, der das Bauelement problemlos zerstören kann. Dieser Durchbruch erzeugt punktförmige Überhitzungen auf der Chipfläche und verschlechtert zumindest die Eigenschaften des Bauteils.

Zerstörung eines Bipolartransistors durch lokale Überhitzung

Des Weiteren gibt es zwei Zerstörungsszenarien, die durch thermische Überhitzung eines Bipolartransistors im leitenden Zustand erfolgen. Während die Überhitzung des Bauteils durch das Abführen der Verlustleistung mittels geeigneter Kühlung vermieden werden kann, besteht die Gefahr eines zweiten Durchbruchs, wenn eine eigentlich zulässig hohe Verlustleistung bei hoher Kollektor-Emitter-Spannung entsteht.

Die gängige Erklärung ist, dass sich die Stromdichte und somit die Verlustleistung in diesem Fall ungleichmäßig auf dem Chip verteilt, was sich aufgrund des positiven Temperaturkoeffizienten der Leitfähigkeit des Halbleitermaterials selbst verstärkt. An den Stellen hoher Verlustleistung überschreitet die Sperrschichttemperatur den zulässigen Wert und der Chip wird zerstört.[1]

Siehe auch

Einzelnachweise

- Area of Safe Operation (ASO). SANYO Semiconductor Co., Ltd, abgerufen am 15. Dezember 2012.