Synchronzähler

Ein Synchronzähler ist ein elektrisches Bauelement der Digitaltechnik, das eine Folge von Ereignissen zählt. Jede dabei entstehende Zahl wird bis zum nächsten Ereignis gespeichert. Der Zählerstand wird im einfachsten Fall in Zahlen des Dualsystems dargestellt. In diesem Fall sind bei vorhandenen binären Speicherelementen die möglichen Zahlen auf beschränkt. Man spricht dann auch von n-bit-Synchronzählern. Durch geeignete Schaltung sind auch Zähler im Dezimalsystem möglich und verbreitet im Einsatz. Das zu zählende Eingangssignal wird bei periodischer Folge auch als Taktsignal bezeichnet.

Synchronzähler gehören zu den synchronen Schaltkreisen, weil sich alle Speicherelemente nur zu einer festgelegten (steigenden oder fallenden) Flanke eines gemeinsamen Signals ändern können. Diese Gleichzeitigkeit über alle Speicherelemente ist dann erforderlich, wenn der Zählerstand von einer elektronischen Einrichtung (z. B. Mikroprozessor) kurz nach dem Ereignis (z. B. nach ½ Periodendauer) übernommen werden soll.

Aufbau

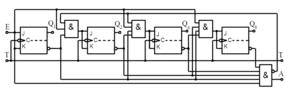

Ein Synchronzähler kann aus JK-Flipflops aufgebaut sein wie in der nebenstehenden Schaltung. Der Triggereingang jedes Flipflops ist hier über den Eingang CLK mit dem Signal des zu zählenden Ereignisses verbunden. Diese Struktur lässt alle Flipflops untereinander synchron laufen und gibt der Schaltung den Namen (im Gegensatz zum Asynchronzähler).

Durch die Verschaltung der Eingänge jedes einzelnen Flipflops können deren Ausgangssignale als eine Ziffernfolge verstanden werden. Im Beispiel steht jeder Ausgang für die Ziffer einer vierstelligen Binärzahl, mit Q0 an niederwertigster Stelle. Durch andere Schaltungen lassen sich beispielsweise vier Flipflops zur Darstellung des 8-4-2-1-Codes einer Dezimalziffer verwenden, siehe Frequenzteiler.

Ein JK-Flipflop verhält sich wie ein T-Flipflop, wenn beide Eingänge denselben Pegel haben. Bei J = K = 1 wechselt der Pegel am Ausgang und bei J = K = 0 bleibt er unverändert. Diese Eigenschaft wird für den Synchronzähler verwendet. Im Folgenden wird ein 4-bit-Vorwärtszähler mit den Ausgängen Q0 bis Q3 beschrieben, der die Zahlen von bis in natürlicher Reihenfolge zählt.

|

|

|

Daraus ergibt sich folgende Verschaltung:

- Das Bit Q0 mit der niedrigsten Stellenwertigkeit (20=1) soll bei jeder steigenden Signalflanke wechseln und wird daher direkt mit dem Takteingang CLK verbunden.

- Das Bit Q1 mit der nächsthöheren Stellenwertigkeit (21=2) soll nur wechseln, wenn der Ausgang Q0 den Pegel 1 hat (also während des vorigen Takts eine 1 ausgegeben hat). Dies wird realisiert, indem der Ausgang mit den J- und K-Eingängen des zweiten Flipflops verbunden wird.

- Das nächste Bit Q2 mit der nächsthöheren Wertigkeit (22=4) soll nur wechseln, wenn alle niederwertigeren Bits (Q0 und Q1) den Pegel 1 haben (also während des vorigen Takt die Binärzahl 11 dargestellt haben). Dies wird mit einem Und-Gatter festgestellt.

- Das letzte Bit Q3 mit der höchsten Wertigkeit (23=8) soll nur wechseln, wenn alle niederwertigeren Bits (Q0, Q1 und Q2) den Pegel 1 haben (also im vorigen Takt die Binärzahl 111 dargestellt haben). Dieses kann mit einem zusätzlichen Und-Gatter realisiert werden, welches das Ergebnis aus dem vorigen Schritt mitverwendet.

Das Beispiel lässt sich auf diese Weise fortsetzen, um beliebig große Zähler zu erzeugen. Wenn, wie in der Erläuterung des letzten Schrittes, vorherige Ergebnisse mit verwendet werden, ist dabei jedoch die Zählgeschwindigkeit massiv eingeschränkt. Um einen korrekten Zustandswechsel des höchstwertigen Bits zu erreichen, muss zum Zeitpunkt der entsprechenden Taktflanke die Information über den Zustandswechsel des niedrigstwertiges Bits von der letzten Taktflanke durch die gesamte Kette von Und-Gattern gewandert sein. Zum Beispiel sorgen die Gatterlaufzeiten der 74HCxx-Serie von Logikbausteinen von typisch 15 ns dafür, dass ein mit nur 10 MHz zählender Synchronzähler der beschriebenen Bauart nicht einmal 8 Bits lang sein kann! – Durch Und-Gatter mit mehreren Eingängen lässt sich die Kettenschaltung aber vermeiden.

Eigenschaften

In der im letzten Abschnitt beschriebenen Bauart summieren sich Gatterlaufzeiten (schaltzeitbedingte Verzögerungen). Dies kann vermieden werden, indem jede Stufe ihr Eingangssignal mit einem eigenen Und-Gatter erzeugt, das alle weniger signifikanten Bits verknüpft. Zum Beispiel benötigt das JK-Flipflop von Bit 7 ein vorgeschaltetes Und-Gatter, das auf sieben Eingängen die Bits Q0 bis Q6 erfasst. In einer solchen Bauweise hat der Synchronzähler gegenüber dem Asynchronzähler den Vorteil, dass sich Gatterlaufzeiten nicht summieren und so höhere Taktraten, bzw. bei gleicher Taktrate größere Zähler möglich sind. Der Preis ist eine deutlich höhere Komplexität, die jedoch in FPGA oder dediziert integrierten ICs problemlos realisierbar ist.

Varianten

Rückwärtszähler

Ein synchroner binärer Rückwärtszähler entsteht, indem in der oben gezeigten Schaltung statt der Q-Ausgänge die Q-Ausgänge verwendet werden. Mit jedem Takt zählt der Rückwärtszähler einen Schritt zurück. Wenn der untere Grenzwert 0 erreicht ist, springt der Rückwärtszähler beim nächsten Schritt wieder auf den Höchstwert.

Eine synchrone Rückwärtszählung in Dezimalzahlen ist ebenfalls möglich. Die gezeigte Schaltung für eine Dezimalziffer lässt sich beliebig kaskadieren. Der BCD-Code wird an den normalen Q-Ausgängen abgegriffen. Zur Zählerfreigabe wird der Eingang E an logisch 1 gelegt; bei den Folgeschaltungen wird E mit A der Vorstufe verbunden. Das zu zählende Signal wird an T gelegt und über alle Stufen durchverbunden. Nach dem Ausgangssignal 00002=010 führt die nächste fallende Flanke an T auf den Wert 10012=910, und ein Übertragszählschritt wird ausgeführt.

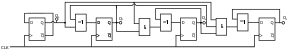

Mit D-Flipflop

Die nebenstehende Schaltung zeigt einen Vorwärtszähler mit D-Flipflops. Sobald alle niederwertiger bewerteten Flipflops auf 1 geschaltet haben (Erkennung durch die Und-Gatter), wird der Eingang des nächsten Flipflops invertiert (durch Rückkopplung des eigenen Zustandes und eine XOR-Verknüpfung mit dem Ergebnis des Und-Gatters). Auch dieses Schema lässt sich ohne Einfluss auf die maximale Zählgeschwindigkeit beliebig fortsetzen, um größere Zähler zu realisieren.

Um aus der gezeigten Logikschaltung einen Rückwärtszähler zu machen, werden die inversen Flipflop-Ausgänge (Qx) für den Zählerstand verwendet. Die restliche kombinatorische Logik zur Ansteuerung der jeweils nachfolgenden Flipflops bleibt unverändert. Auch bei diesem Zähler ist Q0 das niederwertigste Bit (LSB).

Reversibler Zähler

Beispielsweise bei der Positionsmessung mittels Inkrementalgeber sind, wenn beide Bewegungsrichtungen zulässig sind, Zähler erforderlich, die vorwärts und auch rückwärts zählen können. Eine Richtungserkennung muss ein zusätzliches Steuersignal an den Zähler liefern. Schaltungen hierzu werden in der Literatur beschrieben.[1] Diese Zähler sind immer Synchronzähler.

Einzelnachweise

- F. Dokter und J. Steinhauer: Digitale Elektronik in der Meßtechnik und Datenverarbeitung, Band II: Anwendung der digitalen Grundschaltungen und Gerätetechnik. Philips Fachbücher, 3. Aufl. 1973, S. 55 ff