Package-on-Package

Package-on-Package (PoP, engl., wörtlich übersetzt „Gehäuse auf Gehäuse“) ist in der Aufbau- und Verbindungstechnik der Mikroelektronik eine Fertigungstechnik, bei der zwei oder mehr speziell dafür vorbereitete Chipgehäuse, üblicherweise sind dies Ball Grid Array (BGA), übereinander bestückt und in dieser gestapelten Anordnungen auf die Leiterplatte gelötet werden. Diese Bauform erlaubt eine höhere Integrationsdichte als die Anordnung der einzelnen BGA-Gehäuse auf der Leiterplatte nebeneinander und wird bevorzugt in Smartphones, Digitalkameras und Tablet-Computern eingesetzt. PoP wurde im Jahr 2007 bei der Firma Maxim Integrated Products entwickelt und die Art des Aufbaus ist in JEDEC-Standards festgelegt.[1][2]

Allgemeines

Bei Package-on-Package mit zwei Einzelgehäusen muss das untere BGA auf beiden Seiten Anschlusspins aufweisen. Nach unten zur Hauptplatine sind wie bei allen BGA-Gehäusen Balls (engl. für „Lotkügelchen“) aufgelötet, nach oben zu dem oberen BGA-Gehäuse befinden sich entsprechende Lötflächen zur Aufnahme der Anschlusspins vom oberen BGA-Gehäuse. Die beiden BGA-Gehäuse werden getrennt gefertigt und erst unmittelbar vor dem Reflow-Lötprozess übereinander mittels Bestückungsautomaten auf der Leiterplatte bestückt. Da bei dem Lötvorgang die Wärme durch den oberen BGA-Chip hindurch zu dem unteren BGA-Chip gelangen muss, um auch die unten liegenden BGA-Anschlusspins mit der Hauptplatine sicher zu verlöten, andererseits keine Schäden infolge einer Übertemperatur in den Halbleiterchips auftreten dürfen, sind für den Lötprozess entsprechend genaue und abgestimmte Temperaturprofile nötig.

PoP wird üblicherweise in zwei Bereichen eingesetzt:

- Bei zwei oder mehreren Speicherchips. Üblicherweise sind dies hochintegrierte DDR-SDRAM Speicher. Anwendungen liegen in kompakten Speicherkarten oder Speichermodulen.

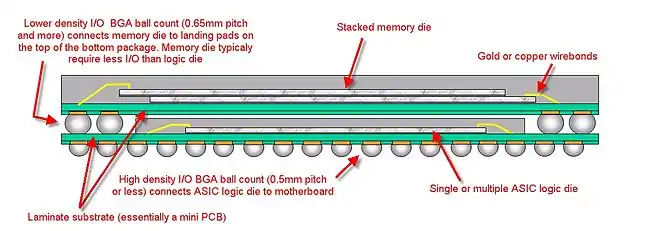

- Die Kombination eines Hauptprozessors (CPU) im unteren Chip und darüberliegend der für das System-on-a-Chip (SoC) notwendige Hauptspeicher, üblicherweise als DDR-SDRAM ausgeführt. Anwendungen dieser Kombination liegen bei mobilen Computersystemen und in folgender Schnittabbildung schematisch dargestellt.

Package-on-Package ist von dem sogenannten System-in-Package (Stacked-Die-Package) zu unterscheiden, bei dem zwei oder mehr Dies, das sind die ungehäusten Halbleiterchips, in einem Chipgehäuse untergebracht werden und nach außen wie ein einziger Chip wirken.[3] System-in-Package finden unter anderem bei Flash-Speichern Anwendung, um die Speicherkapazität pro Chipgehäuse steigern zu können.

Ein Vorteil von Package-on-Package gegenüber System-in-Package besteht darin, dass die einzelnen Chips vor der Bestückung getrennt getestet werden können.[3] Weiters ist im Prinzip bis kurz vor dem Lötprozess die Festlegung einer bestimmten Chip-Kombination möglich. So kann bei Package-on-Package der oben liegende Speicherchip vor dem Lötprozess in der Speichergröße variiert werden. Ein Vorteil von PoP gegenüber Leiterplatten besteht in den kurzen Leiterbahnen zwischen den beiden Chips. Damit können Speicher und die Verbindung zwischen den beiden Chips mit hohen Taktfrequenzen betrieben werden.

Nachteilig an PoP ist die vergleichsweise schlechte Möglichkeit, Abwärme im Betrieb mittels Kühlkörper an die Umgebung abführen zu können. Insbesondere der untere Chip kann seine Abwärme nur schlecht abgeben. Daher ist PoP primär auf Anwendung beschränkt, wo nur eine geringe Verlustleistung auftritt und ein vergleichsweise geringer Stromverbrauch vorhanden ist. Dies ist typischerweise bei mobilen elektronischen Geräten wie Smartphones oder Tablet-Computern der Fall.

Weblinks

- Pan Pacific Symposium Conference Proceedings: PoP (Package on Package): An EMS perspective on assembly, rework and reliability. Abgerufen am 25. November 2012.

Einzelnachweise

- JEDEC Standard Nr. 21-C, Seiten 3.12.2 – 1

- Patent US7923830: Package-on-package secure module having anti-tamper mesh in the substrate of the upper package. Angemeldet am 13. April 2007, veröffentlicht am 12. April 2011, Erfinder: Steven M. Pope, Ruben C. Zeta.

- R. Fischbach, et al.: From 3D Circuit Technologies and Data Structures to Interconnect Prediction. In: Proc. of 2009 Int. Workshop on System Level Interconnect Prediction (SLIP). 2009, S. 77–83, doi:10.1145/1572471.1572485 (PDF).