PCI Express

PCI Express („Peripheral Component Interconnect Express“, abgekürzt PCIe oder PCI-E) ist ein Standard zur Verbindung von Peripheriegeräten mit dem Chipsatz eines Hauptprozessors. 2003 eingeführt ist PCIe der Nachfolger von PCI, PCI-X und AGP und bietet im Vergleich zu seinen Vorgängern eine höhere Datenübertragungsrate pro Pin. Nach ca. 2010 wurden vielfach keine anderen Steckplätze mehr auf Hauptplatinen verbaut und die Vorgänger PCI(-X) und AGP schließlich vollständig abgelöst.[1]

Über die Anwendung für Erweiterungs-Steckplätze hinaus bilden die PCIe-Protokolle inzwischen die Basis für zahlreiche andere Schnittstellen wie SATA Express, M.2, U.2, SAS Express und Thunderbolt sowie für CFexpress und SD Express Memory Cards.

Während ihrer Entwicklung wurde die Schnittstelle „3GIO“ genannt, was für „3rd Generation Input/Output“ steht.

Technik

| Version | 1.0 / 1.1 | 2.0 / 2.1 | 3.0 / 3.1 | 4.0 | 5.0 | 6.0 | 7.0 |

|---|---|---|---|---|---|---|---|

| Release | 2003 | 2007 | 2010 | 2017[2] | 2019[3] | 2022[4] | 2025 |

| Transfergeschwindigkeit | 2,5 GT/s | 5 GT/s | 8 GT/s | 16 GT/s[5] | 32 GT/s[3] | 64 GT/s | 128 GT/s |

| Leitungscode | 8b/10b | 128b/130b | PAM-4 | ||||

| Sicherungscode | Disparity von 8b/10b | keine Datensicherung | CRC+FEC[6] | ||||

| Lanes | Übertragungsrate (Burstrate in GB/s ohne Protokoll-Overhead) | ||||||

| ×1 | 0,25 | 0,5 | 0,985 | 1,969 | 3,938 | 7,529 | 15,059 |

| (×2) | 0,5 | 1,0 | 1,969 | 3,938 | 7,877 | 15,059 | 30,118 |

| ×4 | 1,0 | 2,0 | 3,938 | 7,877 | 15,754 | 30,118 | 60,235 |

| ×8 | 2,0 | 4,0 | 7,877 | 15,754 | 31,508 | 60,235 | 120,471 |

| ×16 | 4,0 | 8,0 | 15,754 | 31,508 | 63,015 | 120,471 | 240,742 |

PCIe ist im Gegensatz zum parallelen PCI-Bus kein geteiltes (shared) Bus-System, sondern besteht aus für jedes Gerät dedizierten Punkt-zu-Punkt-Verbindungen. Einzelne Komponenten werden über Switches verbunden. Diese ermöglichen es, direkte Verbindungen zwischen einzelnen PCIe-Geräten herzustellen, so dass die Kommunikation einzelner Geräte untereinander die erreichbare Datenrate anderer Geräte nicht beeinflusst.

Die einzelnen Punkt-zu-Punkt-Verbindungen von PCI-Express werden durch eine oder mehrere Lanes einer selbstgetakteten seriellen Verbindung ausgeführt. Es gibt kein eigenes Taktsignal, lediglich ein viel geringerer Referenztakt von 100 MHz wird separat übertragen, der allerdings nicht für die Übertragung verwendet wird. Die Taktrückgewinnung erfolgt aus dem Empfangssignal. Dieses ist speziell dafür kodiert (bis PCIe 2.1 nach dem 8b/10b, PCIe 3.0 bis 5.0 eine „Scrambling“-Kodierung, welche 128 Netto-Datenbits jeweils 2 Synchronisations-Bits voranstellt).[7] Ab PCIe 6.0 werden pro Symbol 2 Bit übertragen, neben einem Synchronisationsymbol kommen 32 Symbole für die Fehlererkennung und 24 Symbole zur Vorwärtsfehlerkorrektur dazu.

Für das Senden der Daten werden Parallel-zu-seriell-Wandler und für den Empfang Seriell-zu-parallel-Wandler in den Baugruppen eingesetzt. Trotz dieses sehr abweichenden physischen Aufbaus ist PCIe softwareseitig voll kompatibel zu PCI, so dass weder Betriebssysteme und Treiber noch Anwendungsprogramme angepasst werden müssen.

PCIe ist vollduplexfähig (dual-simplex) und arbeitet je nach Version mit 250, 500, 985, 1969 oder 3938 MB/s pro Lane und Richtung. In der Entwicklungsphase war PCIe 6.0 mit 7529 MB/s pro Lane und Richtung.

Sämtliche Datenübertragungen und sämtliche Signale (z. B. IRQs) auf der PCIe-Verbindung werden in Pakete aufgeteilt. Auf Grund des grundlegend anderen elektrischen Aufbaus und der anderen Übertragungsform sind keine Mischgeräte möglich, die sowohl in PCI- als auch PCIe-Slots betrieben werden könnten. Das ist auch durch andere Anschlüsse bedingt, so dass für PCIe-Karten entsprechend neuere Motherboards bzw. Controller verwendet werden müssen.

PCIe ist wie PCI prinzipiell Hot-Plug-fähig, was das Ein- und Ausbauen von (z. B. defekten) Erweiterungskarten im laufenden Betrieb ermöglicht, sofern die Hardware und auch das Betriebssystem das unterstützen.

Topologien

PCI-Express kann über drei verschiedene elektrische Topologien angebunden sein:

- PCI-Express-Gerät auf der Systemplatine

- PCI-Express-Geräte verbunden über einen Steckverbinder auf der Systemplatine, in dem eine Add-On-Karte steckt

- PCI-Express-Geräte verbunden über zwei Steckverbinder: einen auf der Systemplatine, in dem eine Riser-Karte steckt, und eine oder mehrere Add-On-Karten in den Steckplätzen der Riser-Karte (wird von PCI Express 4 passiv nicht mehr unterstützt).

Letztere weisen neben den Standardbusbreiten auch ×16 (als zwei ×8), ×24 (als drei ×8), ×32 (als zwei ×16) oder ×48 (als drei ×16) auf.

Bei auf dem Markt erhältlichen ×24, ×32 und ×48-Steckplätzen handelt es sich um Riser-Steckplätze zur Aufnahme von Erweiterungskarten, die dann 1 bis 3 PCI ×8- oder ×16-Karten aufnehmen können.

Hauptplatinen haben meist einen speziellen PCIe-Steckplatz für Grafikkarten, englisch PCI Express for Graphics und daher „PEG-Slot“, der meist 16 Lanes (×16) anbindet und mehr Strom bereitstellen kann (75 statt sonst nur 25 Watt, siehe Abschnitt Stromversorgung).[8]

Übertragungsschichten

Die Übertragung wird durch mehrere Schichten dargestellt, von denen jede nur mit den direkt benachbarten Schichten kommuniziert, sowie für die auf dieser Schicht übertragenen Daten eine Fehlererkennung oder -korrektur durchführt.

Die unterste Schicht, der sogenannte Physical Layer, stellt die elektrische Verbindung zwischen zwei direkt miteinander verbundenen Geräten dar. Das sind zum Beispiel ein Endgerät (z. B. eine Einsteckkarte) und der nächstgelegene Switch. Die logische Verbindung („Link“) zwischen diesen Geräten besteht aus 1 bis 16 Lanes. Jede Lane wiederum besteht aus zwei Leitungspaaren, je ein differentielles Paar für das Senden und Empfangen (dual-simplex). Jedes differentielle Leitungspaar wird von Treiberstufen angesteuert, die nach dem Standard HCSL (englisch High Speed Current Steering Logic) ausgeführt sind. Der Leitungswellenwiderstand und die dazu idente Leitungsterminierung besteht aus einem differentiellen Abschluss mit 100 Ω. Seit PCIe Gen2 besteht auch die Option, mit einem Leitungswellenwiderstand von 85 Ω zu arbeiten.[9]

Sämtliche Daten, die zwischen PCIe-Geräten übertragen werden, werden gemischt über diese Leitungen seriell übertragen, im Gegensatz zu PCI gibt es also keine eigenen Leitungen mehr für die Signalisierung von Interrupts. Da das serielle Protokoll jedoch nicht angehalten werden kann, ergibt sich eine etwas höhere und auch schwankende Interruptlatenz als bei klassischem PCI mit dedizierten Interruptleitungen.

Der Data Link Layer überträgt die Datenpakete des Transaction Layers zwischen den beiden Verbindungspartnern. Dazu versieht er diese mit einer Sequenznummer, sowie einem 32-Bit-CRC-Wert, dem sogenannten Link CRC (LCRC). Empfangene Pakete werden dem direkten Verbindungspartner mittels Data Link Layer Packets mitgeteilt, ebenso wie der Zustand des Pakets. Beschädigte oder verlorene Pakete werden vom Verbindungspartner erneut gesendet. Dadurch werden die höheren Layer von elektrischen Übertragungsstörungen entkoppelt.

Der Transaction Layer transportiert letztlich die Nutzdaten zwischen dem logischen Sender und Empfänger, das heißt ohne Berücksichtigung der dazwischenliegenden Switches. Die Transaction Layer Packets (TLP) enthalten im Header eine Kennzeichnung, um was für eine Art von Übertragung es sich handelt. Typische Beispiele sind Schreibzugriffe (Writes) sowie Leseanforderungen (Reads) sowie Leseantworten (Completions). Schreibzugriffe sind sogenannte posted transactions, das heißt, sie werden gesendet und erzeugen auf dem Transaction Layer keinerlei Antwort.

Quality of Service

PCIe bietet als neues Feature gegenüber PCI „Quality of Service“. Dazu werden virtuelle Kanäle „Virtual Channels“ (VC) benutzt, denen eine Priorität „Traffic Class“ (TC) zugeordnet wird. Standardmäßig läuft der Datenverkehr über VC0 mit TC0. Durch die Benutzung von anderen virtuellen Kanälen kann bestimmter Datenverkehr priorisiert werden.

Eine typische Anwendung wäre eine Soundkarte bei der Aufnahme: Kann sie ihre Daten nicht rechtzeitig über die Verbindung weiterschicken, weil die Verbindung anderweitig belegt ist, so läuft früher oder später der Zwischenspeicher der Soundkarte über und es gehen Daten verloren. Für diese Echtzeitanwendung würde man den Datenverkehr priorisieren.

Stromversorgung

links: 8-Pin, rechts: 6-Pin

Ein PCI-Express-Steckplatz kann das daran angeschlossene Gerät mit Strom versorgen. Laut Spezifikation beträgt die gelieferte Leistung für einen gewöhnlichen Steckplatz wie bei PCI maximal 25 Watt, für Low-Profile-Karten höchstens 10 Watt und bei einem PEG-(PCIe-×16)-Steckplatz maximal 75 Watt.[10] Diese maximal 75 Watt sind aufgeteilt in 5,5 Ampere über 12 Volt (66 Watt) und 3 A über 3,3 V (9,9 W). Da das für manche Einsatzzwecke wie Grafikkarten oder USB 3.0-Karten jedoch häufig zu wenig ist, sieht die Spezifikation unterschiedliche Zusatzstecker zur Stromversorgung vor, sogenannte PCI Express (Graphics) Power Supply Connector (auch PEG-Connector oder PCIe-Kabel), die +12 Volt liefern.

Die erste Version der Zusatzstecker hat 6 Pins[11][12] und kann bis zu 75 Watt liefern, wodurch die dem Gerät maximal bereitgestellte Leistung auf 150 Watt steigt, bei Nutzung zweier solcher Stecker auf 225 Watt. In der Spezifikation von PCI Express 2.0 wurde ein neuer Zusatzstecker mit 8 Pins definiert, der maximal 150 Watt führen kann. Für noch höhere Leistungen kann ein zusätzlicher Stecker mit 6 Pins genutzt werden, der weitere 75 Watt zuführt, wodurch die maximale Leistungsaufnahme einer PCI-Express-Karte auf 300 Watt begrenzt ist (75 Watt vom Steckplatz, 150 Watt erster Stecker, 75 Watt zweiter Stecker).[13][12] Leistungsfähigere Grafikkarten, die seit Anfang 2011 auf dem Markt sind, sehen die Verwendung von zwei 8-Pin-Steckern vor. Dadurch erhöht sich die maximal zulässige Leistungsaufnahme auf 375 Watt. (75 Watt vom Steckplatz, 150 Watt erster Stecker, 150 Watt zweiter Stecker).

| 6-Pin (max. 75 W)[14] | 8-Pin (max. 150 W)[15][16][17] | |||||

|---|---|---|---|---|---|---|

| Pin | Beschreibung | Pin | Beschreibung | |||

| 1 | +12 V | 1 | +12 V | |||

| 2 | nicht angeschlossen (meist +12 V) | 2 | +12 V | |||

| 3 | +12 V | 3 | +12 V | |||

| 4 | Sense1 (8-Pin angesteckt) | |||||

| 4 | Masse | 5 | Masse | |||

| 5 | Sense (6-Pin angesteckt) | 6 | Sense0 (6- oder 8-Pin angesteckt) | |||

| 6 | Masse | 7 | Masse | |||

| 8 | Masse | |||||

Wenn ein 6-Pin-Stecker in eine 8-Pin-Buchse gesteckt wird, merkt die Karte am fehlenden Sense1, dass sie über die Kabelverbindung nur 75 W beziehen darf.

12-Pin (max. 600 W) 12VHPWR

Ab PCI Express-5.0 sind für Leistungen bis 450 W neue 12-polige Stecker und für Leistungen bis 600 W neue 12+4-polige Stecker vorgesehen. Der Stecker nennt sich 12VHPWR High Power Connector (H+).

| Pin | Beschreibung |

|---|---|

| 1…6 | +12 V |

| 7…12 | Masse |

| 13 | Card Power Stable |

| 14 | Card Cable Present# |

| 15 | Sense0 |

| 16 | reserved |

Welche Maximale Dauerleistung das Netzteil der PCI Express-5.0 Grafikkarte liefern kann, wird über die Beschaltung der Pin 13 bis Pin 16 des 12VHPWR High Power Connector (H+) Steckers definiert.

| Pin 13 | Pin 14 | Pin 15 | Pin 16 | Maximale Dauerleistung |

|---|---|---|---|---|

| Masse | Masse | Offen | Offen | 600 Watt |

| Offen | Masse | Offen | Offen | 450 Watt |

| Masse | Offen | Offen | Offen | 300 Watt |

| Offen | Offen | Offen | Offen | 150 Watt |

12-Pin (max. 600 W) 12V-2×6

In der PCI Express-5.1 Standardisierung wurde der mit PCI Express-5.0 eingeführte neue 12-Pin-Stecker 12VHPWR aufgrund von Problemen mit der sicheren elektromechanischen Verbindung überarbeitet. Die mechanischen Änderungen umfassen eine Verkürzung der Sense Pins 13–16 um 1,7 mm und eine Verlängerung der Pluspol- und Masse-Pins 1–12 um 0,25 mm. Die Verkürzung der Sense Pins soll verhindern, dass der Kontakt zu ihnen hergestellt wird, bevor der Stecker vollständig eingerastet ist. Die Verlängerung der Pluspol- und Masse-Pins soll die elektrische Kontaktfläche auch bei voll eingestecktem Stecker erhöhen, um die generelle Wärmeentwicklung an den Steckkontakten zu reduzieren.[18]

Die elektrischen Änderungen beschränken sich auf eine geänderte Beschaltung der Sense Pins (in der Tabelle sind die Änderungen fett gedruckt).

| Pin 13 | Pin 14 | Pin 15 | Pin 16 | Maximale Dauerleistung |

|---|---|---|---|---|

| Masse | Masse | Offen | Offen | 600 Watt |

| Offen | Masse | Offen | Offen | 450 Watt |

| Masse | Offen | Offen | Offen | 300 Watt |

| Kurzgeschlossen | Offen | Offen | 150 Watt | |

| Offen | Offen | Offen | Offen | 0 Watt |

Durch diese Maßnahmen soll die Problematik nicht vollständig eingerasteter und dadurch teilweise elektrisch überlasteter Stecker behoben oder zumindest minimiert werden, was beim 12VHPWR-Standard zu vereinzelten Schmorbränden geführt hat.[19]

Slot-Varianten

| Lanes | Anzahl Steckkontakte | Mechanische Länge (mm) | |||||

|---|---|---|---|---|---|---|---|

| links | rechts | gesamt | links | Steg | rechts | gesamt | |

| ×1 | 22 | 14 | 36 | 11,65 | 1,78 | 7,65 | 21,08 |

| ×4 | 42 | 64 | 21,65 | 35,08 | |||

| ×8 | 76 | 98 | 38,65 | 52,08 | |||

| ×16 | 142 | 164 | 71,65 | 85,08 | |||

PCI-Express-Karten und PCI-Express-Steckplätze haben zwei Parameter:

- Die mechanische Länge des Slots: Entsprechend der Länge des Slots oder Steckplatzes spricht man von PCIe ×1, PCIe ×4, PCIe ×8 oder PCIe ×16. Weiterhin gibt es „offene“ Steckplätze, in die man mechanisch beliebig lange Karten stecken kann. Allerdings funktioniert dort die Kartendetektion durch die #PRSNT-Kontakte nicht mehr.

- Die maximal verwendbaren Lanes eines Steckplatzes oder einer PCIe-Karte: Häufig entsprechen sie der mechanischen Länge, können aber auch kleiner, aber niemals größer sein. Häufig anzutreffen sind mechanische ×16-Steckplätze, die elektrisch nur ×4 oder ×8 sind. Insbesondere ist es oft der Fall, dass bei Boards mit mehreren ×16-Steckplätzen diese bei gleichzeitiger Verwendung weniger Lanes bereitstellen (s. u.).

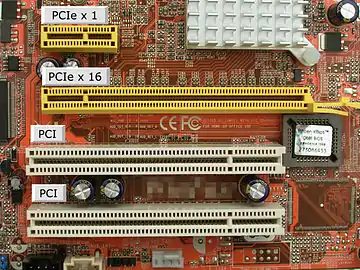

Im Desktopbereich wird meist ×1 als Ersatz für den PCI-Bus und ×16 als Ersatz für den AGP-Steckplatz zur Anbindung von Grafikkarten (gekennzeichneter „PEG-Slot“) verwendet.

Darüber hinaus gibt es noch die PCIe-Varianten ×4 und ×8. ×4 ist vor allem im Serverbereich für Karten mit hohem Durchsatz (Festplattencontroller, 10GE-Netzwerkkarten) zu finden. Die Slots sind außerdem abwärtskompatibel, das heißt eine ×1-Karte kann zum Beispiel auch in einen ×4-Slot gesteckt werden, von den vier Lanes des Steckplatzes wird dann nur eine Lane genutzt. Einige Motherboards besitzen PCIe-Steckplätze ohne abschließenden Steg („offener“ Steckplatz), so dass „größere“ Karten eingesteckt werden können. Sogar das Aufsägen von geschlossenen Slots ist möglich,[20] birgt aber das Risiko, durch die Säge das Mainboard mechanisch zu zerstören. Zudem dürfen keine Mainboard-Bauteile wie Kondensatoren, Stiftleisten, SATA-Anschlüsse oder M.2-Geräte den langen Anschluss an der Karte blockieren.

Möglich ist auch, dass Slots eine von der Bauform abweichende Anbindung der Lanes haben. Dies ist meist der Fall, wenn für SLI und Crossfire zwei (oder mehr) ×16-Slots vorhanden sind und die Hauptplatine beziehungsweise der darauf verwendete Chipsatz keine 32 Lanes für die Grafikkarten bereitstellt. Dann ist der untere Slot langsamer angebunden (meist ×4, oft auch nur mit der vorherigen Generation) und/oder er teilt sich bei seiner Verwendung die Lanes mit dem Hauptslot, was dann nur noch 8 Lanes auf dem Hauptslot ergibt. Allerdings findet in letzterem Fall diese Verminderung der Übertragungskapazität nicht nur bei zwei Grafikkarten statt, sondern beispielsweise auch bei Verwendung einer ×16-Grafikkarte und einer ×1-Karte in diesen Slots, so dass die Grafikkarte nur mit ×8 läuft und 7 Lanes ungenutzt bleiben. Das genaue Verhalten einer Hauptplatine ist in ihren Spezifikationen und im Handbuch vermerkt. Die Reduktion der Lanes senkt die Leistung allerdings bei weitem nicht um den gleichen Faktor: Ein Test zeigte 2011 durch Abkleben der Kontakte einiger der letzten PCIe-2.0-Karten, dass meist nur geringe Leistungseinbußen festzustellen waren. Bis runter auf PCIe 2.0 ×4 war der Verlust meist allenfalls messbar, während sich PCIe 2.0 ×1 insbesondere dann negativ auswirkte, wenn der Speicher der Grafikkarte zu klein war.[21] Ähnlich verhält es sich bei der Reduktion der Bandbreite durch Verwendung vorheriger PCIe-Generationen: Nachdem im Januar 2022 Nvidia die GeForce RTX 3050 mit PCIe 4.0 x8 und AMD die Radeon RX 6500 XT gar nur mit PCIe 4.0 x4 ausstatteten, führten Computermagazine Tests aus, wie sich diese Karten mit dem zu dem Zeitpunkt bei Mainboards und CPUs weit verbreiteten PCIe 3.0 verhielten. Auch hier waren die Auswirkungen gering und vor allem bei unzureichender Größe des Grafikspeichers relevant.[22]

Der Steckplatz ist mechanisch in zwei Bereiche unterteilt: Im linken Bereich befinden sich immer 22 Steckkontakte, die hauptsächlich für die Stromversorgung und die Verwaltungskommunikation (SMBus, JTAG) verantwortlich sind. Im rechten Bereich befinden sich je nach Anzahl der Verbindungen 14 bis 142 Steckkontakte, die für die eigentliche Nutzdatenübertragung und weitere Signale konzipiert sind.

Darüber hinaus gibt es bei Notebooks miniaturisierte Varianten von PCIe, unter anderem ExpressCard, PCI Express Mini Card und M.2 für Erweiterungen wie WLAN und SSD oder als Mobile PCI Express Module für Grafikkarten. Zunächst in Servern, mittlerweile auch in Desktop-Computern und Notebooks werden SSDs auch direkt über PCI-Express angesprochen, siehe U.2 und NVMe. Auch M.2 ist hier inzwischen üblich.

PCIe-Slot (oben, gelb) und PCI-Slots (unten, weiß)

PCIe-Slot (oben, gelb) und PCI-Slots (unten, weiß) mSATA-Steckkarte: Physisch PCI Express Mini Card, Elektrisch SATA: Solid-State-Drive ursprünglich für Notebooks

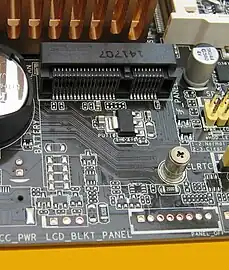

mSATA-Steckkarte: Physisch PCI Express Mini Card, Elektrisch SATA: Solid-State-Drive ursprünglich für Notebooks PCI Express Mini Card-Steckplatz mit Sicherungsschraube

PCI Express Mini Card-Steckplatz mit Sicherungsschraube PCIe-Slot (gelb) für ×1-kompatible Karten, die auch als bis zu ×16 ausgeführt sein können (rechte Seite ist offen)

PCIe-Slot (gelb) für ×1-kompatible Karten, die auch als bis zu ×16 ausgeführt sein können (rechte Seite ist offen)

Pinbelegung

|

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Kompatibilität nach Lane-Anzahl

Der PCIe-Standard verlangt, dass jede Karte eine Verbindung sowohl mit einer Breite von einer Lane als auch mit der elektrisch von der Karte unterstützten Lane-Anzahl herstellen kann. Für Slots gilt das Gleiche. Andere Verbindungsbreiten – der Standard sieht ×1, ×4, ×8 und ×16 vor – sind nicht durch den Standard abgedeckt. Eine Verbindung kommt dann mit der maximalen Breite zustande, die sowohl vom Slot als auch von der Karte unterstützt wird.

Da die elektrische Breite kleiner sein kann als die Bauform und manche Linkbreiten optional sind, ist es nicht offensichtlich, mit welcher Breite eine Karte in einem gegebenen Slot funktionieren wird. Die „PCI Express Label Specification and Usage Guidelines“ von 2006 empfehlen daher, an jedem Slot und auf jeder Karte genau aufzulisten, welche Verbindungsbreiten unterstützt werden. Das wird jedoch nur selten umgesetzt.

|

| |||||||||||||||||||||||||||||||||

Kompatibilität nach PCIe-Versionen

PCIe-Steckkarten und -Steckplätze sind generell abwärtskompatibel zu Gegenstücken aller vorherigen Generationen.[24] Die Übertragung findet dabei jeweils auf Basis des schnellsten gemeinsamen Protokolls statt. Das heißt, dass zum Beispiel eine PCIe-1.0-Karte in einem 3.0-Slot nur mit 2,5 GT/s überträgt, eine PCIe-2.0-Karte im selben Slot dagegen mit 5 GT/s.

Literatur

- Ravi Budruk u. a.: PCI Express System Architecture. Addison-Wesley, Boston 2004, ISBN 0-321-15630-7

- Franz-Josef Lintermann, Udo Schaefer, Walter Schulte-Göcking, Klaas Gettner: Einfache IT-Systeme. Lehr-/Fachbuch. 5, 1. korrigierter Nachdruck Auflage. Bildungsverlag EINS, 2008, ISBN 978-3-8237-1140-7 (Seite 64–66).

Weblinks

- PCI-Express-Spezifikation auf pcisig.com (englisch)

- PCI Express: Kurz erklärt auf tweakpc.de

- PCI Express: Grundlagen auf computerbase.de

- PCIe – PCI Express auf Elektronikkompendium

Einzelnachweise

- Christof Windeck: Abschied vom PCI Local Bus. In: Heise online. 3. Juni 2010. Abgerufen am 27. Februar 2022.; Zitat: „Bei einigen kommenden Chipsätzen der Serie 6 verzichtet Intel auf die Anbindung eines konventionellen PCI-Bus.“.

- PCI-SIG Releases PCIe 4.0, Version 1.0. PCI-SIG, abgerufen am 26. Oktober 2017.

- PCI Express Base Specification Revision 5.0. Abgerufen am 12. Dezember 2018 (englisch).

- https://www.pcwelt.de/article/1954054/pcie-7-0-kommt-frueher.html

- Claire Castellanos Nereus: PCI-SIG Announces PCI Express 4.0 Evolution to 16GT/S, Twice the Throughput of PCI Express 3.0 Technology. PCI-SIG, 29. November 2011, archiviert vom (nicht mehr online verfügbar) am 23. Dezember 2012; abgerufen am 19. Mai 2013 (englisch).

- Für je 256 übertragene Bytes (ein FLIT): 8 Byte CRC für eine einfache Fehlererkennung + 6 Byte für eine Fehlerkorrektur im Fehlerfall. Als Fehlerkorrektur wird häufig in Tabellen FLIT angegeben, allerdings ist das der Name eines Paketes (Flow Control Unit) und nicht die Fehlerkorrektur selbst.

- Benjamin Benz: Steiniger Weg – Wie serielle Interconnects der Physik ein Schnippchen schlagen, c’t 10/2010, S. 188–191.

- Christof Windeck: FAQ: PCI Express. In: Heise online. 14. November 2020. Abgerufen am 27. Februar 2022.; Zitat: „PCI Express for Graphics (PEG) spezifiziert einen PCIe-Steckplatz für Karten mit bis zu 16 PCIe-Lanes, der bis zu 75 Watt Leistung bereitstellt. Andere PCIe-Slots sind für höchstens 25 Watt ausgelegt. Nicht jeder PEG-Slot ist mit den vollen 16 PCIe-Lanes beschaltet.“.

- PCI Express/HCSL Termination Application Note AN-808. Renesas Electronic Cooperation, 2013, abgerufen am 9. März 2022.

- Christof Windeck: Was ist PEG? Wie unterscheiden sich PCI Express und PCI Express for Graphics (PEG)? In: c’t magazin. 2009, abgerufen am 12. Oktober 2010 (Aus c’t 1/09).

- PCI Express Power (6 pin). In: hardwarebook.info. 2007, abgerufen am 12. Oktober 2010 (englisch).

- Reale Leistungsaufnahme aktueller Grafikkarten. PCIe-Stromversorgung – 6/8-Pin-Stecker. In: Hard Tecs 4U. 29. Januar 2009, abgerufen am 12. Oktober 2010 (Grafische Darstellung der Pinbelegung).

- The Quick PCI-Express 2.0 Guide. In: 10stripe.com. Abgerufen am 12. Oktober 2010 (englisch).

- PCI Express x16 Graphics 150W-ATX Specification Revision 1.0

- PCI Express 225 W/300 W High Power Card Electromechanical Specification Revision 1.0

- PCI Express Card Electromechanical Specification Revision 3.0

- Yun Ling: PCIe Electromechanical Updates. 16. Mai 2008, archiviert vom am 5. November 2015; abgerufen am 7. November 2015.

- Igor Wallossek: Rest in Peace 12VHPWR Connector - Willkommen 12V-2×6 Connector, wichtige Modifikationen und PCIe Base 6 | Exklusiv. 3. Juli 2023, abgerufen am 5. August 2023 (deutsch).

- Fabian Vecellio del Monego: Defekte 12VHPWR-Stecker: Nvidia bezieht Stellung und sieht Schuld bei Anwendern. 19. November 2022, abgerufen am 5. August 2023.

- Andreas Link: PCI-E-x16-Grafikkarte in x8-Slot zwängen geht? Geht! In: PC Games Hardware. 12. April 2016, abgerufen am 16. Dezember 2018.

- Wolfgang Andermahr: PCIe-Schnittstellen im Test: x16, x8, x4, x1 – wie viel ist nötig? (Seiten 3–5). In: ComputerBase. 29. August 2011, abgerufen am 16. Dezember 2018.

- Raffael Vötter: Geforce RTX 3050 8GB im Test. In: PC Games Hardware. 27. Januar 2022, abgerufen am 29. Januar 2022.

- What is the A side, B side configuration of PCI cards. In: Frequently Asked Questions. Adex Electronics, 1998, abgerufen am 24. Oktober 2011.

- FAQ: PCI Express 4.0 – Will PCIe 4.0 products be compatible with existing PCIe 1.x, PCIe 2.x and PCIe 3.x products? PCISIG, abgerufen am 11. Februar 2016.