Overlay (Halbleitertechnik)

Der englischsprachige Begriff Overlay bezeichnet im Bereich der Halbleitertechnik die Überdeckungsgenauigkeit von Strukturen aus unterschiedlichen Fertigungsschritten, in der Regel zweier fotolithografischer Ebenen. Es ist ein wichtiger Parameter bei der Fertigung von integrierten Schaltkreisen (ICs), wie Computerprozessoren und Mikrocontrollern, denn Ausrichtungsfehler jedweder Art können Fertigungsfehler, wie Kurzschlüsse oder fehlende Verbindungen, verursachen und somit die Funktionsweise der Schaltung einschränken.

.svg.png.webp)

Neben dem Overlay-Versatz gibt es noch einen etwas anderen Fehler, der bei der Fertigung auftreten kann und im deutschen ebenfalls als Überdeckungs- oder Positionierungsgenauigkeit bezeichnet wird, der registration (englisch). Er beschreibt die Positionierungsgenauigkeit der Strukturen gegenüber einem absoluten Koordinatennetz.

Hintergrund

Die Herstellung von integrierten Schaltkreisen erfolgt durch eine Abfolge von fotolithografischen Strukturierungen sowie nachfolgenden Prozessierungen wie Ätzen und Implantation auf einem Substrat, dem Wafer. Damit der fertige Schaltkreis korrekt funktioniert ist es notwendig, dass die einzelnen fotolithografischen Maskierungen möglichst aufeinander abgestimmt sind und somit die gefertigten Strukturen, zum Beispiel Kontakte, Leitungen und die Bestandteile der Transistoren, möglichst nah an das Ideal der geplanten Schaltkreise-Layouts herankommt.

Messung und Messgeräte

Allgemein

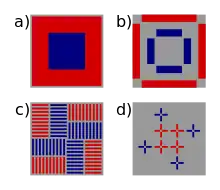

Die Überdeckungsgenauigkeit wird typischerweise mithilfe spezieller Strukturen gemessen, die für diese Aufgabe optimiert wurden. Prinzipiell könnten aber auch die eigentlichen später für die Funktion notwendigen Strukturen verwendet werden. Bei den speziellen Strukturen handelt es sich meist um zwei Strukturen ähnlicher Gestalt aber unterschiedlicher Größe, die im Idealfall zentrisch zueinander angeordnet sind, beispielsweise Box-in-Box-Struktur – dabei handelt es sich um meist quadratische übereinanderliegende flächige Strukturen, die in Z-Richtung häufig durch eine dritte Ebene getrennt sind. Die Messung erfolgt durch Abstandsmessungen der jeweiligen Strukturkanten. Aus dem Mittelwert des „linken“ und „rechten“ bzw. des „oberen“ und „unteren“ Abstands ergeben sich die Overlay-Werte für die x- bzw. y-Achse an der gemessenen Position auf dem Wafer.

Die Messung erfolgt in der Regel durch optische Messgeräte und mittel- bis langwelligem Licht – energiereicheres kurzwelliges Licht würde ähnliche Effekte haben wie das bei der Belichtung eingesetzte UV-Licht und somit die Fotolackmaske negativ beeinflussen. Hersteller von Messgeräten für die Massenproduktion sind unter anderem KLA Corporation (ARCHER-Serie) und Nanometrics (CALIPER-Serie).

Teststrukturen / Overlay-Marken

Die Overlay-Teststrukturen sind mit Seitenlängen von ca. 15 µm verhältnismäßig groß (im Belichtungsfeld können sie auch eine Seitenlänge von nur 5 µm haben). Box-in-Box-Marken mit großflächigen Strukturen werden daher seit dem Einsatz der chemisch-mechanischen Planarisierung zur Einebnung der Waferoberfläche nach der Schichtabscheidung kaum noch eingesetzt. Denn hier kann das sogenannte dishing – ein übermäßiger Materialabtrag in großen Strukturen – auftreten und somit das lokale Planarisierungsergebnis negativ beeinflusst. Dies kann zu Problemen bei nachfolgenden Fertigungsschritten wie der Herstellung der zweiten Ebene der Overlay-Struktur führen. Aus diesem Grund wurden neue Teststrukturen eingeführt, die weniger groß sind und mehr den eigentlichen Strukturen auf dem Wafer entsprechen. Dazu zählen Linienstrukturen wie Frame-in-Frame (engl. frame, dt. ‚Rahmen‘) und Bar-in-Bar (engl. bar, dt. ‚Streifen‘ oder ‚Strich‘) sowie Kombinationen daraus wie Box-in-Frame. Weitere industrieübliche Teststrukturen sind Gitterstrukturen wie „AIM“ (advance imaging metrology) und „µAIM“ von KLA-Tencor sowie Grabenstrukturen wie „Blossom“[1] und „µBlossom“ von IBM/Nanometrics.

Neben diesen eigentlichen Overlay-Marken gibt es seit einigen Jahren Teststrukturen die auf der Streuung von Licht an Grabenstrukturen basieren (engl. diffraction-based overlay). Dabei werden Techniken der sogenannten Scatterometrie eingesetzt, die bereits breite Anwendung in der Halbleitertechnik findet, beispielsweise zur Prozesskontrolle bei der Fertigung von Gräben. Dazu gehören unter anderem „SCOL“-Marken (scatterometry overlay) von KLA Tencor. Die neue Overlay-Messtechnik soll stabiler arbeiten und genauere Messwerte liefern. Nachteilig ist der höhere Platzbedarf, was vor allem vor dem Hintergrund zunehmender Messungen im Belichtungsfeld, wo ungern kostbare Fläche für Teststrukturen freigegeben wird, den Einsatz behindert.

Einflussgrößen

Neben dem eigentlichen Overlay-Versatz treten in der Praxis zusätzliche Einflüsse durch den Wafer und dem Messsystem auf. Sie können in symmetrische und asymmetrische Größen unterteilt werden. Symmetrische Einflüsse sind beispielsweise Änderungen der Strukturgrößen, allgemein als kritische Abmessung (engl. critical dimension, CD) bezeichnet, auf. Damit sind vor allem Breitenvariationen verbunden, durch die symmetrische Gestaltung der Messmarken (targets) und der Mittelwertbildung aus der „linken“ und „rechten“ Verschiebung, lassen sich diese Einflüsse eliminieren. Anders hingegen asymmetrische Einflüsse, sie können wenn überhaupt nur durch zusätzliche Messungen reduziert werden. Asymmetrische Einflüsse lassen sich in durch das Messgerät und durch den Wafer verursachte Verschiebungen unterteilen und werden auch im Deutschen mit den englischen Abkürzungen TIS (tool-induced shift) und WIS (wafer-induced shift) bezeichnet. Die Wechselwirkungen zwischen diesen Einflüssen sind komplex.

Tool-induced shift (TIS)

Beim TIS (engl. tool-induced shift, dt. Anlagen-verursachte Verschiebung) handelt es sich um eine vom Messgerät (engl. tool) verursachte Verschiebungen zwischen den beiden Teilwerten aus der Overlay-Bestimmung und führt zu einem verfälschten Messwert. Die Ursache für das Auftreten des TIS sind die in der Realität immer auftretenden Toleranzen bei der Einrichtung des optischen Systems. Sie führen beispielsweise dazu, dass die „Blickrichtung“ des Messgerätes nicht genau senkrecht auf den zu messenden Wafer ist. Dadurch kommt es zu einer Verschiebung der beiden Teilwerte (ein Teilwert wird etwas größer und der andere entsprechend kleiner). Da dieser Einfluss annähernd als stabil betrachtet werden kann, wird er in der Regel als systematischer Fehler bei der Messung angesehen. Der TIS für eine Struktur lässt sich verhältnismäßig leicht bestimmen, in dem dieselbe Struktur nochmals um 180°-gedreht gemessen wird. Bei einem idealen Messsystem würde der bei 180° gemessene Overlay-Wert genau dem Betrag der Messung bei 0° entsprechen, aber jeweils entgegengesetzte Vorzeichen besitzen. Bei einem realen Messsystem kommt, wie erwähnt, der TIS hinzu. Er lässt sich durch die Addition der Overlay-Werte aus beiden Messungen bestimmen:

Vernachlässigt man weitere Einflüsse durch den Wafer oder die Wafer-Halterung, so kann man vereinfacht annehmen, dass der TIS für alle Messungen gilt und so können die Messwerte nach der Bestimmung des TIS’ an wenigen Messmarken durch Subtraktion korrigiert werden. Mit zunehmenden Genauigkeitsanforderungen an die Messung gewinnen weitere Parameter, wie die Wafergeometrie, an Bedeutung, da auch sie Einfluss auf den TIS haben. Die Korrektur dieser Einflüsse, macht es daher zunehmend notwendig, den TIS an deutlich mehr oder gar an allen Messstellen zu bestimmen.

Neben den physikalisch bedingten Einflüssen durch das Messgerät hat auch die Bildauswertung des Overlay-Messgeräts (größeren) Einfluss auf den TIS. So können kontrastarme Kamerabilder einer oder beider Teststrukturen (Mess- und Referenzebene) sowie ein schlechter/ungeeigneter Kantenerkennungsalgorithmus den TIS zusätzlich erhöhen. Overlay-Anlagen sind daher meist mit unterschiedlichen Farbfiltern ausgestattet. Sie erlauben es den Kontrast des aufgenommenen Graustufenbildes für die Teststrukturen zu variieren und so die Bildauswertung bzw. den TIS vor das entsprechende Messrezept zu optimieren.

Wafer-induced shift (WIS)

Wie bereits erwähnt, gibt es unterschiedliche Overlay-Teststrukturen, die alle von asymmetrischen Einflüssen der Teststrukturen auf die Fertigungsprozesse herrühren, beispielsweise eine asymmetrische Schichtabscheidung. Die hierdurch verursachten weniger systematischen Messfehler werden als wafer-induced shift[2] (engl., WIS, dt. „Wafer-verursachte Verschiebung“) bezeichnet und können einen wesentlichen Teil des gesamten Messfehlers ausmachen. Im Gegensatz zu TIS können die WIS-Einflüsse nicht einfach durch mehrfache Messung derselben Struktur bei unterschiedlichen Drehwinkeln bestimmt werden. Sie sind allgemein recht schwer identifizierbar bzw. bestimmbar. Oft können sie erst nach den Folgeprozessen bestimmt werden, beispielsweise nach dem Ätzen einer von der Fotolackmaske maskierten Schicht.

Darstellung

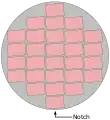

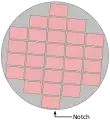

Die Darstellung des Overlay-Versatzes erfolgt häufig in Form einer Vektorkarte des Wafers. In dieser Karte werden an der Position der Messstellen die Vektoren für den x- und y-Versatz angetragen. Auf diese Weise lassen sich leicht einfache Overlay-Fehler wie Translation oder Rotation sowie Ausreißer bei den Messwerten erkennen.

Analyse und Modellierung

Bei der Produktion von Halbleiterprodukten fließen zahlreiche nach einem Prozessschritt ermittelte Messdaten in die Korrektur von Prozessparametern nachfolgender Werkstücke (Wafer) ein, vgl. statistische Prozessregelung (SPC) und gehobene Methoden der Prozessführung (APC). Zu diesen Parametern zählen auch Overlay-Informationen, die während der Produktion oder in speziellen Experimenten ermittelt wurden. Über unterschiedliche komplexe Korrekturmodelle fließen diese Daten durch die Software der Belichtungsanlagen direkt in den Fertigungsprozess ein, beispielsweise in Form von Änderungen in der Waferposition oder der Waferausrichtung.

Die Modellierung des Overlay-Versatzes und die Ermittlung von Korrekturdaten kann allgemein in Fehler, die vom Reticle und die durch den Wafer bzw. den Wafertisch verursachte werden, unterteilt werden. Die Formen dieser beiden Gruppen von Overlay-Fehlern sind wiederum abhängig vom eingesetzten Fotolithografiesystem, das heißt, ob eine Anlage, die nach dem Ganzwafer-, Scanner-, Step-and-Repeat- oder Step-Scan-Prinzip arbeitet, verwendet wird.

Neben diesen grundlegenden Overlay-Fehler gibt es noch zwei weitere große Gruppen Fehlerursachen. Dies sind zum einen Fehler, die durch den Einsatz mehrerer Belichtungsanlagen entstehen (sogenannte Matching-Fehler) zum anderen prozessabhängige Effekte. Bei Matching-Fehler handelt es sich um Unterschiede zwischen verschiedenen Belichtungsanlagen (Abstimmungsfehler). Dabei handelt es sich um nicht-zufällige Fehler, die beispielsweise durch Unterschiede in der Präzision der Positionierungssysteme oder durch Nichtplanaritäten der eingesetzten Interferometerspiegel entstehen. Prozessabhängige Effekte sind wiederum Einflüsse, die durch Änderungen des Ausrichtungssignals der Ausrichtungsmarken entstehen. Verursacht werden sie durch das Zusammenspiel aller an der Fertigung beteiligten Prozessparameter, wie z. B. Ätztiefe, Schichtabscheidung oder Polierprozesse. Sie wirken sich auf die Gestalt der Ausrichtungsmarken aus. Sie können beispielsweise zu asymmetrischen Ausrichtungsmarken führen, die sich bei der Messung als Versatz zeigen, der real jedoch nicht vorhanden ist.

Grundmodell

Der einfachste Fall einer Fotolithografieanlage ist das „Ganzwafer“-Prinzip, bei dem der Wafer mit einem Schritt vollständig mit der Maske belichtet wird; Dieses Urprinzip wird in der Regel für Wafergrößen mit einem Durchmesser bis zu 100 mm eingesetzt. Betrachtet man nur die Positionierung des Reticles und des Wafers zueinander, so können hierbei folgende Formen von Overlay-Fehlern auftreten: 1. relative Verschiebung in x- bzw. y-Richtung, 2. eine Rotation und 3. eine trapezförmige Verzerrung durch ein Verkippung. Die Ursachen hierfür liegen in Positionierungs- und Ausrichtungsfehlern des Reticles oder des Wafers. In Projektionssystemen bei denen die Strukturen auf der Maske größer sind als die abgebildeten Strukturen kann zusätzlich noch ein Vergrößerungsfehler auftreten, der durch unterschiedliche Fokuseinstellungen verursacht wird.

Mathematisch können diese Einflüsse durch ein einfaches lineares Modell erfasst werden:

und

Wobei und der Overlay-Versatz in x- bzw. y-Richtung ist, der sich aus einem absoluten Versatz und , dem Skalierungsfehler bzw. , dem Rotationsanteil bzw. und den nicht korrigierbaren Restfehlern und zusammensetzt.

Besonderheiten von Scanner- und Stepper-Systemen

Bei Scanner-Systemen erfolgt die Belichtung des Wafers ebenfalls in einem Schritt. Jedoch wird hierbei nicht der ganze Wafer simultan belichtet, sondern die Belichtung erfolgt nur in einem streifenförmigen Bereich der über den Wafer geführt wird. Dazu werden das Reticle und der Wafer in einer Achse gegenläufig bewegt. Diese zusätzliche Bewegung kann wiederum zwei wesentliche Formen des Overlay-Fehlers verursachen: eine asymmetrische Vergrößerung in Richtung der Bewegungsachse, der durch unterschiedliche Bewegungsgeschwindigkeiten Führungssysteme hervorgerufen wird, und einen Schräglauf (engl. skew), der durch Parallelitätsfehler zwischen den beiden Führungssystemen verursacht wird.

- Auswirkungen einer relativen Verdrehung von Reticle und Wafer um 5°

Verursacht durch eine Drehung des Reticles

Verursacht durch eine Drehung des Reticles Verursacht durch eine Drehung des Wafers

Verursacht durch eine Drehung des Wafers

Problematisch bei diesen beiden Anlagentypen ist, dass aus den Messdaten allein nicht bestimmt werden kann, ob der Fehler nun durch das Reticle oder den Wafer verursacht wurde. Denn es wird nur der Overlay-Versatz der beiden relativ zueinander bestimmt. Anders sieht dies bei Stepper-Systemen (Step-and-Repeat-Prinzip) aus. Hier erfolgt die Belichtung, indem das Reticle mehrfach hintereinander in einem Raster auf den Wafer abgebildet wird. Durch diesen Unterschied zeigen sich die Ausrichtungsfehler von Reticle und Wafer auf unterschiedliche Art. So zeigt sich beispielsweise eine Rotationsverschiebung des Wafers stark abhängig von der Position des Belichtungsfeldes auf dem Wafer, das heißt, der Betrag des Overlay-Fehlers ist in den Randbereichen des Wafers am größten und in der Mitte theoretisch gleich null (siehe Abbildung). Zusätzlich treten bei Steppern neben Positionierungs- und Ausrichtungsfehlern des Reticles bzw. des Wafers weitere Fehlerursachen auf, die durch den eingesetzten Waferhalter (engl. chuck) verursacht werden. Hierbei sind unter anderem Nichtlinearitäten in einer Achse als auch Nichtorthogonalitäten der Achsen zueinander zu nennen. Sie zeigen sich wiederum in Translations- und Rotationsfehlern. Relevant sind diese vor allem beim Einsatz mehrerer Anlagen. Dabei ist es egal ob es sich dabei um baugleiche oder unterschiedliche Anlagentypen handelt, denn die Positionierungsfehler des Wafertisches sind individuell und können sich auch bei Wartungsarbeiten geändert haben. Das heutzutage (2012) in der industriellen Produktion hauptsächlich eingesetzte Step-Scan-Prinzip stellt einen Hybrid aus Scanner und Stepper dar, siehe Stepper (Halbleitertechnik). Hier treten alle der zuvor genannten Overlay-Fehler auf.

Weitere Einflüsse

Neben diesen verhältnismäßig einfachen Ursachen für Overlay-Versätze spielen in modernen Anlagen (fast immer Step-Scan-Prinzip) noch weitere Fehlerquellen eine Rolle. Hierzu zählen beispielsweise Unebenheiten des Wafertisches oder Linsenverzerrungen. Dies sind in der Regel Overlay-Fehler höherer Ordnung mit verhältnismäßig kleinen Beträgen. Sie können aber gerade bei Produkten mit Strukturgrößen von unter 45 nm entscheidend für die Qualität sein, da sie den entscheidenden Anteil an dem verbleibenden Overlay-Fehler nach der Korrektur der genannten Fehlerursachen ausmachen und sich in den kritischen Bereichen (Gate-Strukturierung und die ersten Leiterbahnebenen) bemerkbar machen. Aufgrund der höheren Ordnung sind deutlich mehr Messdaten für die Modellierung notwendig, die zudem nicht mehr nur aus dem mit Ritzgraben (scribe line), sondern auch aus dem Bereich der eigentlichen Schaltung stammen müssen. Aufgrund des hohen Messaufwandes und der Tatsache, dass sich die Werte meist nur bei Umbaumaßnahmen an den Anlagen ändern, werden die Daten nicht in der laufenden Produktion ermittelt. Ein weiterer Nachteil bei der Bestimmung der höhergradigen Fehler ist, dass die Overlay-Strukturen im Vergleich zu den aktiven Strukturen sehr groß sind, dies stellt einen sehr hohen und somit kostenintensiven Flächenbedarf dar.

Weitere Einflüsse, die problematisch bei der Herstellung moderner Schaltkreise sind, sind minimale Längenänderungen durch Temperaturunterschiede von Teilen der Belichtungsanlage oder des Wafers. Diese sind jedoch durch Overlay-Modelle nur schwer korrigierbar, da hier der Betriebszustand eine wichtige Rolle spielt. Diese Einflüsse werden daher durch entsprechende Aufwärmzeiten und definierten Prozesstemperaturen minimiert.

Bedeutung

Die Overlay-Kontrolle hat in den letzten Jahren deutlich an Bedeutung gewonnen und ähnlich kritisch wie die Kontrolle der CD-Werte. Ursachen hierfür sind die aufgrund der industrietypischen Skalierung der Strukturen steigende Strukturdichte sowie der zunehmende Einsatz von komplexen Fertigungstechniken wie die Doppelstrukturierung (engl. double patterning), die mit der 45-nm- und nachfolgender Technologieknoten in die Fertigung eingeführt wurden.

Literatur

- Chris A. Mack: Principles of optical lithography. Wiley, 2007, ISBN 978-0-470-01893-4, S. 314–326 (englisch).

- Harry J. Levinson: Principles of Lithography. 3. Auflage. SPIE Press, 2011, ISBN 978-0-8194-8324-9, Kapitel 6: Overlay (englisch).

Weblinks

- M. David Levenson: KLA Tencor announces Archer 200 overlay metrology system. electroiq, abgerufen am 6. Dezember 2011 (Beispielbild für einen Overlay-Fehler).

- Chin-Chou Kevin Huang, David Tien: Overlay control goes to high-order. electroiq, abgerufen am 6. Dezember 2011 (Beispiele mit Overlay-Vektor-Karten von Wafern, die Registrations- und Wafer-bezogene Fehler anzeigen.).

Einzelnachweise

- C. P. Ausschnitt u. a.: Blossom overlay metrology implementation. Band 6518. SPIE, 2007, S. 65180G, doi:10.1117/12.712669.

- Prosenjit Rai-Choudhury (Hrsg.): Handbook of microlithography, micromachining, and microfabrication. Institution of Engineering and Technology, London 1997, ISBN 0-85296-906-6, S. 500–501.