Low Voltage Differential Signaling

Bei dem englischen Begriff Low Voltage Differential Signaling (LVDS) handelt es sich um einen Schnittstellen-Standard für Hochgeschwindigkeits-Datenübertragung. LVDS ist standardisiert nach ANSI/TIA/EIA-644-1995. Es beschreibt die physische Schicht, nicht die höheren, darauf aufsetzenden Protokoll-Schichten.

Wichtige physikalische Merkmale sind:

- differenzielle Spannungspegel

- relativ geringe Spannungspegel (englisch low voltage)

- die Signale werden mit einer Konstantstromquelle erzeugt

Anwendungen

Die hauptsächlichen Anwendungen liegen bei seriellen Hochgeschwindigkeitsübertragungen mit einigen GBit/s. Typische Anwendungen von LVDS sind Serial ATA (SATA), FireWire, HyperTransport, Videoschnittstellen wie DisplayPort und auch Feldbusse wie SpaceWire und RapidIO. Weiterhin basieren - meist proprietäre - digitale Schnittstellen von Flüssigkristallbildschirmmodulen im Embedded-Anwendungsbereichen und bei Laptops, wo das Display fest im Gehäuse integriert ist, auf LVDS.

Digitale Videoschnittstellen zwischen PC und einem externen Monitor, wie Digital Visual Interface (DVI) oder HDMI, basieren hingegen auf physikalischer Ebene auf dem prinzipiell ähnlichen, aber für längere Übertragungsdistanzen optimierten Transition-Minimized Differential Signaling (TMDS). Die seriellen Hochgeschwindigkeitsverbindungen bei PCI Express basieren auf der High Speed Current Steering Logic (HCSL).

Spannungspegel

Low voltage (niedrige Spannung) bedeutet, dass statt einer üblichen hohen Spannung (high voltage) für digitale Systeme von 5 V oder 3,3 V eine niedrigere Spannung verwendet wird. Dies hat mehrere Vorteile. Bei klassischen Schnittstellen wie EIA-422 ist eine relativ hohe Leistung notwendig, um die Ladung des Kabels zu ändern. Die dabei auftretenden Spannungsänderungen (hohes dU/dt) und hochfrequenten Lade- und Entladeströme (hohes dI/dt) gehen einher mit hochfrequenten elektrischen (E-Feld) und magnetischen Feldern (H-Feld), welche starke elektromagnetische Störungen darstellen. Die hochfrequenten Umladungsströme sorgen zusätzlich auf den Stromversorgungsleitungen für Probleme. Die immer weitere Strukturverkleinerung moderner Halbleiter bringt zudem eine Herabsetzung der Versorgungsspannungen mit sich. Bei hohen Datenraten kommt man daher an einer Verkleinerung des Signalpegels nicht vorbei. LVDS arbeitet mit einem Spannungshub von 350 mV. Differenzielle Signalübertragung bedeutet, dass zwei Leitungen verwendet werden und die Differenz der Spannungen für den Logikzustand ausschlaggebend ist. Bei LVDS beträgt der Unterschied 350 mV, während die absolute Spannung gegen Masse bei etwa 1200 mV liegt. Ein Logikwechsel wird durch entgegengesetzte Änderungen der Spannung auf beiden Leitungen erzeugt. Dies wird als symmetrische Signalübertragung bezeichnet. Dabei liegt immer eine Leitung auf dem High-Pegel und die andere Leitung auf dem Low-Pegel, bei einer Signalpegeländerung wechseln also beide.

| Vee | VOL | VOH | Vcc | VCMO |

| GND | 1,0 V | 1,4 V | 2,5–3,3 V | 1,2 V |

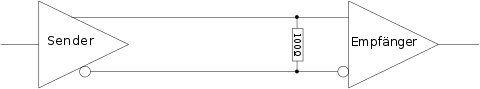

Funktionsprinzip

Auf der Treiberseite erzeugt eine Konstantstromquelle einen Strom von 3,5 mA. Dieser wird, abhängig vom Logikpegel des Eingangssignals, zwischen den beiden Signalleitungen umgeschaltet. Dabei wird die jeweils andere Leitung mit dem Nullpegel verbunden. Auf Empfängerseite fließt der Strom durch einen Abschlusswiderstand von 100 Ω. Dieser Wert entspricht dem Wellenwiderstand der Leitung. Dadurch wird eine Reflexion zurück zur Signalquelle weitgehend vermieden. Der Signalstrom erzeugt im Empfänger eine Spannungsänderung von +350 mV zu −350 mV und umgekehrt.

Layout (Leiterbahnführung)

Die niedrigen Spannungspegel bewirken, dass LVDS-Signale gegenüber elektromagnetischen Störungen absolut empfindlicher sind. Ein geeignetes Layout kann der Störempfindlichkeit jedoch entgegenwirken:

Es empfiehlt sich Hin- und Rückleiter eng beieinander zu führen oder einen Leiter über einer Massefläche derart zu gestalten, dass sich durch die Geometrie und das Dielektrikum der Leiterplatte der gewünschte Leitungswellenwiderstand einstellt. Durch die geringe Fläche, welche die dicht beieinander geführten Leiter aufspannen, kann nur ein geringer magnetischer Fluss eines störenden elektromagnetischen Feldes einwirken und damit nur eine geringe Spannungsdifferenz in der Leitung erzeugen. Zudem äußert sich diese überwiegend als Gleichtaktstörung und gegenüber dieser sind die Empfänger bei LVDS-Übertragung bis zu 1 V tolerant, da beide Signalspannungen um den gleichen Wert verändert werden, ohne die Bereichsgrenzen zu erreichen. Dadurch wird letztlich eine höhere Störsicherheit erzielt.

Die eng beieinander geführten Leitungen bewirken umgekehrt auch eine nur geringe Abstrahlung des Gegentakt-Nutzsignals. Trotzdem können sich bei unzweckmäßiger Ausführung einer Schaltung auch entlang einer gut geführten Leitungsanordnung unerwünschte Gleichtaktsignale einstellen, die zur ungewollten Abstrahlung einer elektromagnetischen Welle führen. Diese lassen sich aber durch eine insgesamt EMV-gerechte Gestaltung der Schaltung und nicht nur durch die Leitungsführung beeinflussen.

Bei Übertragungsstrecken im GBit/s-Bereich sind Laufzeitunterschiede zwischen den Pfaden und eventuell auch zu anderen LVDS-Kanälen des gleichen Busses zu vermeiden. Gleiche Leiterlängen sind daher zu einer synchronen Signalübertragung erforderlich. Diese Bedingung kann u. a. mit mäandrierenden Leiterzügen erreicht werden.

LVDS wird häufig als einer von mehreren Signalstandards für die Ein- und Ausgangskanäle in FPGAs integriert. Hier geben Hersteller wie Xilinx die Leitungslängen innerhalb der Gehäuse als sogenannte „Flight-Time“ an. Die Bezeichnung suggeriert zwar eine Zeitangabe, es handelt sich aber um die Leitungslängenangabe in Millimetern.

Datenraten

Die maximale Datenrate einer LVDS-Schnittstelle hängt von der Kabelqualität ab. Mit Cat-5-Kabel UTP ist typischerweise eine Leitungslänge von etwa 2 m bei einer Datenrate von 200 MBit/s möglich. Für verdrillte, abgeschirmte Leitungspaare im Bereich unter 50 cm für z. B. den Anschluss von Displays sind typisch 500 MBit/s erwartbar. Nach dem derzeitigen Stand der Technik liegt die Grenze bei mehreren GBit/s.

Siehe auch

Einzelnachweise

- Interfacing Between LVPECL, VML, CML and LVDS Levels (PDF; 259 kB), abgefragt am 20. Februar 2015, engl.