Mehrfachstrukturierung

Unter Mehrfachstrukturierung (englisch multiple patterning) werden in der Halbleitertechnik verschiedene Strukturierungsverfahren für die Herstellung sehr dichter und feiner Strukturen zusammengefasst. Die meisten Verfahren basieren auf einer fotolithografischen Strukturierung (in der Regel die anspruchsvolle Immersionslithografie) mit doppeltem Abstandmaß (engl. pitch) der gewünschten Strukturen. Prinzipiell können so die erzielbaren Strukturgrößen gegenüber Einfachstrukturierung halbiert werden; wobei im Fall der Immersionslithografie die erreichbaren Strukturgrößen bereits unterhalb der eigentlichen Auflösungsgrenze der für die Abbildung verwendeten Wellenlänge liegen.

Die einfachste Variante ist die Doppelstrukturierung (englisch double patterning), wobei auch unter diesem Begriff unterschiedliche Techniken zusammenfasst werden, siehe unten. Die Doppelstrukturierung wurde in der Halbleiterindustrie Mitte bis Ende der 2000er-Jahre beim 32-nm-Technologieknoten eingeführt, da mit den damaligen Fertigungsverfahren (193-nm-Fotolithografie und Immersionslithografie) die Abbildung von Fotolackstrukturen bei einem Half-Pitch von 45 nm nicht mehr ausreichend scharf[1] abgebildet werden konnten. Da die Fotolithografietechniken der nächsten Generation damals zu teuer waren bzw. noch nicht für die Produktion mit hohen Stückzahlen zur Verfügung standen, ermöglichte die Doppelstrukturierung eine verhältnismäßig „einfache“ und „kostengünstigere“ Fertigung von Strukturen höherer Strukturdichten mit konventionellen Fotolithografieanlagen. Die Technik wird seitdem in verschiedenen Formen eingesetzt. Die Verfahren der Mehrfachstrukturierung stellen in der Regel Erweiterungen bzw. Kombinationen von Einzeltechniken dar, die bereits bei der Doppelstrukturierung angewendet werden.[2]

Die Mehrfachstrukturierung gehört zur Gruppe der Auflösungsverbesserungsverfahren (engl.: resolution enhancement technique, RET), welche bei Strukturgrößen unterhalb der Lichtwellenlänge (193 nm) zum Einsatz kommen.

Grundansätze

Mehrfach-Belichtung

Mehrfachbelichtung (engl. multiple exposure) ist eine spezielle fotolithografische Methode, bei der eine Sequenz von mindestens zwei separaten Belichtungsschritten mithilfe unterschiedlicher Fotomasken und einem abschließenden Ätzschritt durchgeführt werden. Die einfachste Form der Mehrfachbelichtung ist die Doppelbelichtung (engl. double exposure) mit einer abschließenden Ätzung[3], die nochmals in zwei Formen unterteilt werden kann:[4]

- zwei Belichtungsschritte an derselben Fotolackschicht mit unterschiedlichen Fotomasken (Sequenz: Fotolackauftrag, Belichtung 1, Belichtung 2, Entwicklung) und abschließender Ätzung

- zwei getrennte vollständige Fotolithografieschritte mit zwei Fotolackschichten inklusive Entwicklung nach der ersten Belichtung (Sequenz: Fotolackauftrag 1, Belichtung 1, Entwicklung 1, Fotolackauftrag 2, Belichtung 2, Entwicklung 2) und abschließender Ätzung

Eingesetzt wird diese Technik im Allgemeinen für Strukturmuster, die sehr unterschiedlich aussehen oder unvereinbare Strukturdichten bzw. -abstände aufweisen. Solche Muster können beispielsweise in zwei Muster unterschiedlicher Orientierung (z. B. um 90° verdreht) zerlegt werden.

.svg.png.webp)

Problematisch bei der Verwendung der Mehrfachbelichtung ist der auftretende Overlay-Versatz (Überlagerungsversatz) zwischen den Strukturen bzw. Strukturteilen der unterschiedlichen Belichtungsschritte. Der Overlay-Versatz entsteht, da die zwischen den beiden Belichtungsschritten geänderten Komponenten des optischen Systems nie perfekt aufeinander ausgerichtet werden können (Beispielursachen: Maskenjustierung, Wafertopografie, Fokus, Belichtungsdosis, thermische Ausdehnung usw.).

Eine Variante des Mehrfachbelichtungsansatzes ist das sogenannte „resist freezing“[5] (dt. ‚Fotolack-Erstarrung‘, engl. auch Litho, Freeze, Litho, Etch, LFLE). Diese Technik erlaubt die Beschichtung der bestehenden Fotolackschicht mit einer zweiten Fotolackschicht. Die JSR Corporation demonstrierte diesen Ansatz für die Herstellung von 32 nm breiten Linien und Zwischenräume. Dabei wurde die Erstarrung durch eine Oberflächenhärtung der ersten Lackschicht erreicht.[6]

Direktschreib-Elektronenstrahllithografie ist von Natur aus eine Mehrfachbelichtungstechnik, da der Elektronenstrahl unterschiedlich geformt und an mehreren Standorten auf den Fotolack projiziert wird.

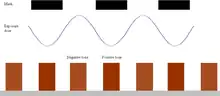

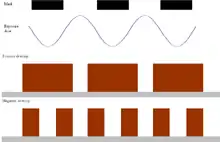

Doppelbelichtung und Doppelätzung

Die Doppelbelichtung und Doppelätzung (engl. double exposure, double etch[7], DEDE, auch DE/DE oder DE², manchmal auch engl. litho etch litho etch, LELE, genannt) ist eine weitere Doppelstrukturierungstechnik, die bereits eingesetzt wird. Anders als bei der zuvor beschriebenen Doppelbelichtung folgt hier nach jedem Belichtungsschritt ein Ätzprozess, bei dem das Muster der jeweiligen Belichtung in das unter dem Fotolack befindliche Material übertragen wird. Dies kann sowohl die eigentlich zu strukturierende Schicht, z. B. Polysilizium für spätere Gate-Elektroden, als auch Hilfsschichten, die als Hartmasken dienen, sein. Als Ergebnis dieser Folge aus Belichtung, Ätzung, Belichtung und Ätzung erhält man eine strukturierte Schicht, in der die Strukturmuster der ersten und der zweiten Fotomaske vereinigt sind.

Die Möglichkeit die Strukturen des ersten Belichtungsschrittes in einer weiteren Schicht (der Hartmaske) fixieren zu können, ist ein wesentlicher Vorteil des DEDE-Ansatzes gegenüber der einfachen Doppelbelichtung. Die hierbei auftretenden Wechselwirkungen zwischen den Bildern beider Belichtungsschritte in derselben Fotolackschicht können mit dem DEDE-Ansatz ausgeschlossen und auf diese Weise höhere Strukturdichten als mit Doppelbelichtung allein hergestellt werden.

Durch die Verschachtelung der beiden Teilmuster kann dabei die Strukturdichte theoretisch unbegrenzt erhöht werden, der Half-Pitch ist hierbei umgekehrt proportional zur Anzahl der verwendeten Teilmuster. Zum Beispiel kann ein 25-nm-Half-Pitch-Muster durch zwei 50-nm-Half-Pitch-Muster, drei 75-nm-Half-Pitch-Muster oder vier 100-nm-Half-Pitch-Muster erzeugt werden. Die Verkleinerung der Strukturen wird höchstwahrscheinlich die Hilfe von weiteren Techniken wie chemical shrinks, thermal reflow oder shrink assist films benötigen. Praktisch sind dieser Methodik jedoch Grenzen gesetzt, z. B. erhöhte Variation in der Fertigung und höhere Kosten mit jeder weiteren Stufe.

Auch bei dieser Technik können hinsichtlich Anzahl der Hartmasken- und Planarisierungsschichten, eingesetzter Fotolacktyp, gewählter Maskierungs-Ansatz[8] (Herstellung von Linien oder Gräben in der Hartmaske) usw. weitere Unterverfahren unterschieden werden. Im Folgenden sollen zwei Prozessfolgen mit und ohne Einsatz einer Hartmaske[9] exemplarisch beschrieben werden.

Linienverdopplungsansatz

Bei der klassischen DEDE-Strukturierung, vgl. Abbildung rechts, wird zunächst auf dem zu strukturierenden Material/Substrat eine zusätzliche Opferschicht abgeschieden, die später als Hartmaske dient. Diese Hartmaske wird nach einem normalen Fotolithografieschritt (Resistauftrag, Belichtung und Entwicklung des Fotolacks/Resists) geätzt. Dabei wird die Struktur der Fotomaske in die Hartmaskenschicht übertragen. Nach der Entfernung der ersten Fotolackmaske folgen die zweite fotolithografische Strukturierung mit einer anderen Fotomaske und eine erneute Ätzung der Hartmaske. So entsteht ein Muster, das sich aus den Strukturen der neuen Fotolackschicht und der Hartmaske zusammensetzt und durch einen anschließenden anisotropen Ätzprozess in die darunterliegende Zielschicht bzw. Zielschichtstapel übertragen werden kann.

Diese Technik ermöglicht theoretisch eine Verdoppelung der Strukturdichte, wie es das Interuniversity Microelectronics Centre (IMEC, Belgien) zur Strukturierung der Gate-Ebenen mit einem 32-nm-Half-Pitch-Prozess demonstrierte.[10] Ähnlich wie bei der Doppelbelichtung erfolgen auch bei diesem Ansatz die beiden Teil-Strukturierungen mehr oder weniger unabhängig voneinander. Die bei der Fertigung auftretenden Toleranzen zwischen dem zweiten Fotolackmuster und dem ersten Hartmaskenmuster resultieren in einer zusätzlichen Abstandsvariation.

Grabenverdopplungsansatz

Das nebenstehende Bild zur Herstellung von dicht zusammen liegenden Grabenstrukturen zeigt einen DEDE-Ansatz ohne Hartmaske. Wie zu sehen ist, wird hierbei keine Opferschicht aufgetragen und das Muster des ersten Belichtungsschrittes wird durch Ätzen des darunterliegenden Materials direkt in die Zielschicht übertragen. Diese Prozessfolge wird anschließend wiederholt und man erhält wiederum eine strukturierte Schicht, die die Muster der beiden Belichtungsschritte vereinigt.

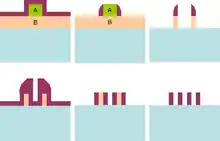

Self-aligned (spacer) double pattering (SaDP)

_double_pattering_(SaDP).svg.png.webp)

Als Spacer (dt. ‚Abstandshalter‘) werden dünne strukturierte Schichten an der Seitenwand vorhandener Strukturen bezeichnet. Sie werden durch konforme Abscheidung, das heißt gleichförmig an allen Flächen inkl. den Seitenwänden, einer Schicht auf einer zuvor strukturierten Oberfläche und anschließendem anisotropen Ätzen (Materialabtrag senkrecht zur Oberfläche) der Schicht gebildet. Durch diese Prozessfolge entstehen zwei neue Strukturen: jeweils ein Abstandhalter an der linken und rechten Seite der ursprünglichen Struktur. Durch entsprechende Prozessbedingungen (vor allem die abgeschiedene Schichtdicke) kann man eine Verdoppelung der ursprünglichen Liniendichte erzielen. Damit ermöglicht die Spacer-Technik die Herstellung von engen Gate-Strukturen mit der Hälfte des ursprünglichen lithographischen Linienabstands.

Der Spacer-Ansatz ist insofern einzigartig, als dass mit einer einzigen lithographischen Belichtung die Linienbreite unabhängig von der Abfolge der Spacer-Bildung und der Struktur-Übertragungs-Prozesse halbiert werden kann. Auf diese Weise wird das ernste Problem der sehr geringen Overlay-Toleranzen zwischen aufeinander folgenden Belichtungen umgangen. Die notwendige Kontrolle und Homogenität der Schichtdicke über den gesamten Wafer und unabhängig von den lokalen Strukturdichten stellt jedoch eine Herausforderung dar, die in der Hochvolumenproduktion nicht zu vernachlässigen ist.

Als Spacer-Materialien werden allgemein Hartmasken-Materialien wie Siliciumnitrid oder Siliciumdioxid eingesetzt. Sie zeigen nach dem Ätzen qualitativ besserer Strukturen als Fotolackmasken, die in der Regel durch höhere Kantenrauigkeiten geprägt sind.[11]

Neben der Schichtdickenkontrolle sind die wichtigsten Themen beim Spacer-Ansatz:

- Bleiben die Spacer erhalten, nachdem das Material der ursprünglichen Struktur, an die sie gebunden sind?

- Ist ihr Profil akzeptabel?

- Wird das darunterliegende Material beim Entfernen der Spacer angegriffen?

Die Strukturübertragung ist in der Hinsicht kompliziert, dass bei der Spacer-Herstellung auch ein wenig des darunter liegenden Materials entfernt wird (Überätzung). Dies ist notwendig damit keine Materialreste in Bereichen übrigbleiben, die frei bleiben sollen. Dieser Ansatz führt aber zu einer leicht höheren Topographie des Substrates auf der in den freien und durch den Spacer bzw. Dummy-Gate geschützten Bereichen.[12] Dies führt zu zusätzlichen Herausforderungen an die Fertigung für nachfolgende Prozessschritte, der Feineinstellung der elektrischen Transistorparameter und der Strukturierung selbst, falls der SaDP-Ansatz mehrfach durchgeführt werden sollte.

Zweitonfotolacke

Vor einigen Jahren wurden sogenannte Zweitonfotolacke (engl. dual-tone photo-resist) entwickelt, die es ermöglichen, nach der Belichtung/Abbildung einer einzelnen Linienstruktur (engl. line) zwei benachbarte Linienstrukturen zu erzeugen. Erste Demonstrationen dieser Technik nutzten Fotolacke, die von sich aus unlöslich im Entwickler waren (was auch die Belichtung mit geringen Dosen nicht änderte) und bei denen gleichzeitig hohe Dosen eine Vernetzungsreaktion bewirkten, die sie ebenfalls unlöslich machten.[13] Alternativ dazu kann ein Fotobasegenerator bei hohen Dosen „Säurelöscher“ erzeugen, die der Reaktion entgegensteht, die den Fotolack löslich macht.[14][15] Aufgrund der Einfachheit und Wirtschaftlichkeit dieses Ansatzes, konnten die fotolithografischen Fähigkeiten aktueller Fotolacke ausgeweitet werden.

Zweiton-Entwicklung

Zweiton-Entwicklung[16] (engl. dual-tone development, DTD) ähnelt der zuvor beschriebenen Zweitonfotolack-Technik und ermöglicht ebenfalls die Herstellung von vervielfältigten Strukturen ohne eine zusätzliche Belichtung, ein Beispiel ist ein von Fujifilm[17] entwickelter Prozess. Im Unterschied zur Zweitonfotolack wird der Fotolack jedoch zweimal entwickelt. Im erstens Schritt entfernt ein Entwickler (beispielsweise das konventionell eingesetzte TMAH) die mit einer hohen Strahlendosis belichteten Bereiche. Der zweite Schritt nutzt ein chemisch anders wirkendes Lösungsmittel, wie Wasser oder ein organisches Lösungsmittel, das die unbelichteten oder mit niedriger Strahlendosis belichteten Bereiche entfernt. Die eingesetzten Lösungsmittel werden unter anderem abhängig von der Fotolackchemie und dem Fotolacktyp ausgewählt und können sich deutlich von den genannten Chemikalien unterscheiden. Unabhängig davon, welche Lösungsmittel eingesetzt werden, ist das Ergebnis eines erfolgreichen Prozesses, dass die mit mittlerer Dosierung belichteten Bereiche stehen bleiben, bei dem jede Kante von jeweils einem Teilentwicklungsprozess erzeugt wird. Eine zentrale Herausforderung hierbei ist es, nicht nur Prozessfenster für die Einzelentwicklungen zu zeigen, sondern auch eine ausreichende Fensterüberlappung sicherzustellen. Bis heute (2010) wurde eine solche Überschneidung nur in Simulationen und nicht experimentell gezeigt.

Kombinationen

Neben der Doppelstrukturierung ist der Mehrfach-Spacer-Ansatz die derzeit am häufigsten veröffentlichte Mehrfachstrukturierungs-Methodik, der in vielen Formen praktiziert werden kann.[18][19][20] Es ist aber auch möglich, zwei oder mehr der oben genannten Ansätze zu kombinieren. Zum Beispiel die Nutzung eines Zweiton-Fotolacks mit pitch-halbierten Säureprofil in Kombination mit einer Zweiton-Entwicklung, die die höchsten und niedrigsten Säurekonzentrationen löst. Dies würde theoretisch eine Verbesserung des Pitch-Auflösung um den Faktor 8 ermöglichen, beispielsweise die Skalierung eins 40 nm breiten Half-Pitch auf 5 nm. Darüber hinaus könnte man mit einer wiederholten Spacer-Ansatz die Auflösung um den Faktor 16 verbessern, womit ein 40 nm breiter Half-Pitch auf 2,5 nm reduziert werden könnte. Die praktische Umsetzung vor allem in der Volumenproduktion solcher theoretischer Ansätze ist jedoch anspruchsvoll und wurde selbst in Labormaßstab bislang kaum/nicht gezeigt.

2D-Layout-Überlegungen

Die Erhöhung der Strukturdichte für 2D-Muster ist sehr stark abhängig von der Art des Musters. Zum Beispiel haben Kontaktfelder, das heißt größere Bereiche, in denen sich eine Vielzahl von Löchern für die Kontaktierung von Source, Drain und Gate vorhanden sind, als rechteckige Felder eine optimale Packungsdichte für die Doppelstrukturierung, hexagonaler Anordnungen eignen sich hingegen optimal für eine Dreifachstrukturierung – dabei wird näherungsweise eine zweimal beziehungsweise dreimal bessere Flächenausnutzung erzielt. Bei 2D-Layouts treten Fehler bei der Einhaltung von Designvorschriften für die Doppelstrukturierung auf, wenn ungerade Perioden der kleinsten Abstände vorhanden sind. Dies kann durch eine Lockerung der Größe einer dieser Abstände auf einen Wert gelöst werden, an dem beide Strukturen im selben Belichtungsschritt abgebildet werden können. Hingegen geht die Dreifach-Strukturierung konform mit einer ungeraden Periode, aber sie eignet sich wiederum nicht für die Herstellung zweier gegenüberliegender Linienendenpaaren, bei denen der Ecke-zu-Ecke-Abstand geringer als der Abstand einer Einfachstrukturierung ist. Dies wiederum geht konform mit einer Vierfachstrukturierung. Die Verbesserung der Strukturdichte unter Einsatz der Mehrfachstrukturierung ist somit in hohem Maße abhängig vom jeweiligen Muster. Oft können einfache Designänderungen oder entspannte Größenvorgaben in eine Richtung den Aufwand und die Kosten vermeiden, die bei komplexeren und teureren Mehrfachstrukturierungsprozessen entstehen.[21]

Anwendungen

Aufgrund seiner eher einfachen Anwendung, das heißt, ohne die Notwendigkeit die industrielle Infrastruktur zu ändern, werden einfache Formen der Mehrfachstrukturierung voraussichtlich auch in Zukunft auf nur geringe technische oder ökonomische Barrieren stoßen. Trotz der Bedenken hinsichtlich der Kosten und des Durchsatzes haben diese Techniken in letzter Zeit (Stand 2010) mehr Aufmerksamkeit und Interesse bekommen. Dies hat auch, mit den Verzögerungen in der nächsten Generation von Lithografietechniken wie EUV- und Nanoprägelithografie zu tun.

Mehrfachstrukturierung kann auch in High-Bias-Prozessen (z. B. Fotolack-Trimmen um Linienbreiten oder Fotolack-Reflow, um Grabenbreiten zu reduzieren) genutzt werden, um die Defektdichte für ein Design-Pitch von 2× oder kleiner zu reduzieren. In Anbetracht des steigenden Auflösungsvermögens der Fotolithografieanlagen, was zu generell zu einer höheren Defektdichte auf den Wafern führt, ist dies ein wesentlicher Vorteil.

Fotolithografie

Die Doppelstrukturierung wird seit einigen Jahren von vielen größeren Halbleiterherstellern (Intel, Globalfoundries, TSMC etc.) für die Fertigung der von Gate-Strukturen eingesetzt, beispielsweise Intel bei Logik-Produkten in 65-nm- und 45-nm-Technik.[22][23] Beispielsweise kommt dabei eine DEDE-Variante zum Einsatz, bei der im ersten Teilschritt ein dichtes Linienmuster in einer Hartmaske fixiert wird und im zweiten Schritt diese Linien „zugeschnitten“ werden (engl. cut). Typisch für einen solchen Prozess, sind Strukturen mit sehr rechtwinkligen[24] Linienenden. Mit einem Einfach-Fotolithografieprozess ist dies Endenform aufgrund von Beugungseffekten mit denselben Anlagen und Strukturgrößen nicht erreichbar – auch nicht wenn OPC-Techniken zum Einsatz kommen. Die Extrapolation der Doppel- zur Mehrfachstrukturierung wurde bereits in Betracht gezogen, wird aber weiterhin durch das Problem der Kostenkontrolle begrenzt. Des Weiteren werden zwar die Vorteile der Mehrfachstrukturierung in Bezug auf Auflösung, Tiefenschärfe und lithographischen Defektsensibilität verstanden, aber es gibt derzeit noch Fragen hinsichtlich der Kontrolle der Prozessbudgets-Erhöhung und der Aufrechterhaltung einer guten Ausbeute.

Auch zukünftige Logikprodukte könnten durch eine Mehrfachstrukturierung den Einsatz der 193-nm-Immersionslithografie hergestellt werden. So zeigte Intel Forschungsergebnisse für die 11-nm-Technik (entspricht einem Pitch von 20–22 nm), bei dem 5 Belichtungsschritte mit insgesamt 5 Masken eingesetzt wurden.[25] Dabei wurde eine Belichtung mit Spacer-Strukturierung genutzt, um eine weitere Pitch-Aufteilung zu erzielen. Die restlichen vier Belichtungen wurden hingegen wieder für das Beschneiden der Pitch-geteilten Linien verwendet. Dies ist erwähnenswert, da auch bei Lithografieverfahren der nächsten Generation wie EUVL oder maskenloser Direkt-Elektronenstrahllithografie weiterhin ein zweiter Belichtungsschritt für das Abschneiden der Linien notwendig wäre.

Das IMEC hat angedeutet, dass im Fall einer weiterhin nicht einsatzbereiten EUV-Lithographie die Vierfachstrukturierung (mit engeren Overlay-Spezifikationen) für die Herstellung zukünftiger Bauelemente verwendet werden könnte.[26]

Bei den 2010er Flash Memory Summit wurde abgeschätzt, dass die Immersionslithographie mit Mehrfachstrukturierung verwendet wird, um innerhalb weniger Jahre NAND-Flash-Speicher auf Strukturbreiten unterhalb 20-nm-Skala zu skalieren.[27]

Elektronenstrahllithografie

Wie bereits erwähnt, ist die Elektronenstrahllithografie von Natur aus eine Mehrfachbelichtungstechnik. Aber auch Elektronenstrahllithografie würde letztendlich mindestens zwei verbundene Belichtungsschritte erfordern (durch Sekundärelektronen-Streuung), zum Beispiel bei der Herstellung von Röntgenzonenplatten mit einem Half-Pitch von 15 nm.[28] In der Tat ist es möglich, dass die Doppelstrukturierung sogar für den Sub-12-nm-Half-Pitch-Bereich nicht ausreichend sein kann, auch nicht mit der Elektronenstrahllithografie.[29][30] In diesem Fall wäre eine Mehrfachstrukturierung notwendig.

Einzelnachweise

- Tokuyuki Honda, Yasuhiro Kishikawa, Yuichi Iwasaki, Akinori Ohkubo, Miyoko Kawashima, Minoru Yoshii: Influence of resist blur on ultimate resolution of ArF immersion lithography. In: Journal of Microlithography, Microfabrication, and Microsystems. Band 5, 2006, S. 043004, doi:10.1117/1.2397018.

- Carlos Fonseca, Mark Somervell, Steven Scheer, Wallace Printz, Kathleen Nafus, Shinichi Hatakeyama, Yuhei Kuwahara, Takafumi Niwa, Sophie Bernard, Roel Gronheid: Advances and challenges in dual-tone development process optimization. SPIE, 2009, S. 72740I, doi:10.1117/12.814289.

- vgl. Michael Lercel: 2006 Lithography Update. (PDF) In: ITRS Winter Conference 2006. 2006, S. 9, archiviert vom (nicht mehr online verfügbar) am 15. Juli 2014; abgerufen am 12. Mai 2013.

- Yayi Wei, Robert L. Brainard: Advanced Processes for 193-nm Immersion Lithography (= SPIE Press monograph. Band 189). SPIE Press, Bellingham 2009, ISBN 978-0-8194-7557-2, S. 215 (englisch).

- S. Kusumoto u. a.: Double Patterning with Resist Freezing Process. In: Workshop on Optical Lithography at 22nm and 16nm. 15. Mai 2008 (Vortragsfolien als PDF (Memento vom 14. Juli 2014 im Internet Archive)).

- Mark LaPedu: JSR demos 'freezing material' for 22-nm production.eetimes, 13. März 2008.

- Rasit Onur Topaloglu, Peng Li: Recent Topics on Modeling of Semiconductor Processes, Devices, and Circuits. Bentham Science Publishers, 2011, ISBN 978-1-60805-074-1, S. 11–13.

- vgl. M. Maenhoudt, D. Vangoidsenhoven, T. Vandeweyer, R. Gronheid, J. Versluijs, A. Miller: Double Patterning process development at IMEC. (PDF) In: Litho Forum 2008. 2008, S. 4, archiviert vom (nicht mehr online verfügbar) am 14. Juli 2014; abgerufen am 12. Mai 2013.

- vgl. Michael Lercel: 2006 Lithography Update. (PDF) In: ITRS Winter Conference 2006. 2006, S. 8, archiviert vom (nicht mehr online verfügbar) am 15. Juli 2014; abgerufen am 12. Mai 2013.

- Double patterning lithography (Memento vom 11. Dezember 2010 im Internet Archive). IMEC, 2007.

- Xuefeng Hua, S. Engelmann, G. S. Oehrlein, P. Jiang, P. Lazzeri, E. Iacob, M. Anderle: Studies of plasma surface interactions during short time plasma etching of 193 and 248 nm photoresist materials. In: Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures. Band 24, 2006, S. 1850–1858, doi:10.1116/1.2217973.

- Yang-Kyu Choi, Ji Zhu, Jeff Grunes, Jeffrey Bokor, Gabor. A. Somorjai: Fabrication of Sub-10-nm Silicon Nanowire Arrays by Size Reduction Lithography. In: J. Phys. Chem. B. Band 107, Nr. 15, 2003, S. 3340–3343, doi:10.1021/jp0222649.

- Patent US6114082: Frequency doubling hybrid photoresist having negative and positive tone components and method of preparing the same. Veröffentlicht am 5. September 2000.

- Soyoung Song, Shoichi Yokoyama, Shigeru Takahara, Tsuguo Yamaoka: Novel dual-mode photoresist based on decarboxylation by photogenerated base compound Novel dual-mode photoresist based on decarboxylation by photogenerated base compound. In: Polymers for Advanced Technologies. Band 9, Nr. 6, 1998, S. 326–333, doi:10.1002/(SICI)1099-1581(199806)9:6<326::AID-PAT785>3.0.CO;2-5.

- Xinyu Gu u. a.: A New Materials-based Pitch Division Technique A New Materials-based Pitch Division Technique. In: Journal of Photopolymer Science and Technology. Band 22, Nr. 6, 2009, S. 773–781, doi:10.2494/photopolymer.22.773.

- Yayi Wei, Robert L. Brainard: Advanced processes for 193-nm immersion lithography. SPIE Press, 2009, ISBN 978-0-8194-7557-2, S. 249–251 (Abschnitt 9.6 Novel Approaches).

- Katherine Derbyshire: Double development offers simpler double patterning. In: Solid State Technology. Band 51, Nr. 5, 2008, S. 18–20 (HTML).

- Andrew Carlson, Tsu-Jae King Liu: Negative and iterated spacer lithography processes for low variability and ultra-dense integration. Band 6924. SPIE, 2008, S. 69240B, doi:10.1117/12.772049.

- B. Degroote u. a.: Spacer defined FinFET: Active area patterning of sub-20 nm fins with high density. In: Microelectronic Engineering. Band 84, Nr. 4, 2007, S. 609–618, doi:10.1016/j.mee.2006.12.003.

- Yang-Kyu Choi: Sub-lithographic patterning technology for nanowire model catalysts and DNA label-free hybridization detection. Band 5220. SPIE, 2003, S. 10–19, doi:10.1117/12.505409.

- Beom-Seok Seo u. a.: Double patterning addressing imaging challenges for near- and sub-k. SPIE, 2009, S. 73791N-73791N-10, doi:10.1117/12.824300.

- D. Vogler: Intel product launch event yields more insight into its manufacturing strategy. In: Solid State Technology (jetzt ElectroIQ). November 2007, archiviert vom (nicht mehr online verfügbar) am 30. Juli 2012; abgerufen am 23. November 2011.

- C. Auth u. a.: 45nm High-k+ metal gate strain-enhanced transistors. In: Intel Technology Journal. Vol. 12, Nr. 2, 2008, S. 77–86, doi:10.1109/VLSIT.2008.4588589 (download.intel.com (Memento vom 10. Juli 2012 im Internet Archive) [PDF]).

- Intel 45 nm process at IEDM (Memento vom 24. März 2009 im Internet Archive)

- Yan Borodovsky: ArF lithography extension for critical layer patterning. LithoVision 2010, 21st Feb.,San. Jose, CA/USA (2010). Zitiert nach: Intel Sr. Fellow Recommends Complementary Solutions for ArF Extension (Memento vom 14. Juli 2011 im Internet Archive). Nikon Precision Inc. 2010.

- Peter Clarke: EUV litho keeps progressing, keeps slipping. EETimes, 9. Juni 2010.

- Garry Tessler: Enabling MLC Flash SSD In Enterprise Storage. 2010 Flash Memory Summit (Vortrag, Vortragsfolien online (Memento vom 11. Juli 2011 im Internet Archive))

- Erik Anderson, Weilun Chao: Double exposure makes dense high-resolution diffractive optics. In: SPIE Newsroom. 2007, doi:10.1117/2.1200702.0599.

- Weilun Chao, Jihoon Kim, Senajith Rekawa, Peter Fischer, Erik Anderson: Hydrogen silsesquioxane double patterning process for 12nm resolution x-ray zone plates. In: Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures. Band 27, 2009, S. 2606–2611, doi:10.1116/1.3242694.

- Weilun Chao, Erik H. Anderson, Peter Fischer, Dong-Hyun Kim: Toward sub-10-nm resolution zone plates using the overlay nanofabrication processes. In: Proc. SPIE. Band 6883, 2008, S. 688309, doi:10.1117/12.768878.